#### 64-189

# Projekt: Entwurf eines Mikrorechners

https://tams.informatik.uni-hamburg.de/ lectures/2025ws/projekt/mikrorechner

- Einführung -

Andreas Mäder, Norman Hendrich

Universität Hamburg Fakultät für Mathematik, Informatik und Naturwissenschaften Fachbereich Informatik

Technische Aspekte Multimodaler Systeme

30. Oktober 2025

## Organisation

Organisation

Motivation

Systemrealisierui

weiteres vorgen

Termine

Zeit Donnerstag, 14:00 – 18:30 Uhr Raum F-522 + F-525

- 1. Plenum

- Einführung am Anfang

- Vorstellung von (Zwischen-) Ergebnissen

- praktische Arbeit in Kleingruppen

Selbstorganisation der Arbeitsgruppen

- Info im Moodle

https://lernen.min.uni-hamburg.de

lokale Web-Seiten

https://tams.informatik.uni-hamburg.de/lectures/2025ws/projekt/mikrorechner

Motivation

Systemrealisierui

weiteres vorgene

- Entwurf und Programmierung eines Mikrorechners

- Schnittstelle zwischen Assembler-Befehlen (ISA) und Hardware

- aktuelle Architekturkonzepte

- RISC-artiger Befehlssatz (Load-/Store-Architektur)

- Assemblerbefehle in Pipeline verarbeiten

- Pipeline Forwarding

- Sprungvorhersage

- Superskalarität (parallele Ausführungseinheiten)

- Caches

- virtueller Speicher

- Interrupts

- Stack

..

### Rechnerarchitektur

ganisation Motivation

Systemrealisierun

weiteres vorgenei

#### Zwei Aspekte der Rechnerarchitektur

- Hardwarestruktur: Art und Anzahl der Hardware-Betriebsmittel und deren Verbindungsstruktur

- = Mikroarchitektur, hier z.B. Harvard-Architektur

- 2. Operationsprinzip: das funktionelle Verhalten der Architektur

- = ISA Instruction Set Architecture

- = Programmierschnittstelle

- ⇒ Möglichkeiten zur Arbeit in dem Projekt

### Arbeit in dem Projekt

ganisation Motivation

Systemrealisierui

weiteres vorgenei

- 1. Hardware-Bezug

- VHDL-Implementation der zugrundeliegenden Architektureinheiten

- Simulation der Hardwareeinheiten

- Synthesewerkzeuge zur Implementation

- 2. Software-Bezug

- Assembler

- Demonstrations- / Anwendungsprogramm

- Compiler

- Betriebssystemfunktionalität

## Realisierung des Systems

Organication

Motivation

Systemrealisierung

weiteres vorgenen

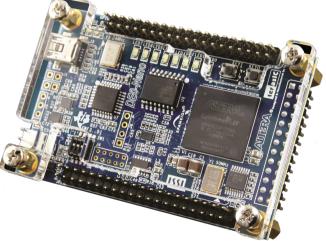

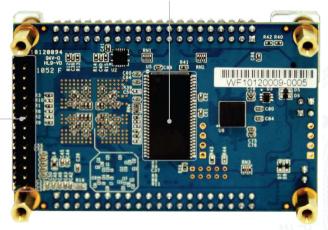

### FPGA-Prototypenplatine

Organisation Motivation Systemrealisierung weiteres Vorgehen

### Field Programmable Gate Array

"Programmierbare Hardware": kann durch Konfiguration so geschaltet und verbunden werden, dass sich beliebige Netzlisten aus logischen Gattern, Flipflops, Addierern, etc. realisieren lassen

- 1. Schaltnetze ⇒ boole'sche Funktionen

- 2. Schaltwerke  $\Rightarrow$  endliche Automaten

- 3. komplexe Systeme  $\Rightarrow$  Prozessoren, etc.

Organisation Motivation **Systemrealisierung** weiteres Vorgeher

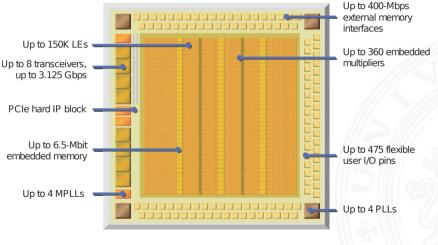

### Altera CycloneIV

## FPGA (cont.)

Systemrealisierung Register Chain Register Bypass LE Routing from LAB-Wide Synchronous LAB-Wide previous LE Programmable Load Synchronous Reaister LE Carry-In Clear data 1 -Row, Column. data 2-► And Direct Link Synchronous Look-Up Table Carry data 3 ---Load and Routing (LUT) Chain Clear Logic ENA CLRN data 4 -Row, Column, And Direct Link Routing labclr1 labclr2 Asynchronous Chip-Wide Local Clear Logic Routing Reset Register Feedback (DEV CLRn) Clock & Register Chain Clock Enable Output Select labclk1-LE Carry-Out labclk2labclkena1labclkena2Motivation

Systemrealisierung

weiteres Vorgehei

- programmierbare Hardware: FPGA

- Cyclone IV EP4CE22F17C6N [60 nm Prozess, 2009]

- 153 I/O Pins, gesamt 256 Pins

- 22 320 LEs ≈ 270 000 Gatter

- 594 Kbit (interner) Speicher

- 66 HW-Multiplizierer: 18 × 18 bit

- 4 PLLs

- On-Board Speicher

- 32MB SDRAM

- 2Kbit I<sup>2</sup>C EEPROM

- Konfiguration

- über USB Schnittstelle

- Power-On Konfig. aus Flash (EPCS64)

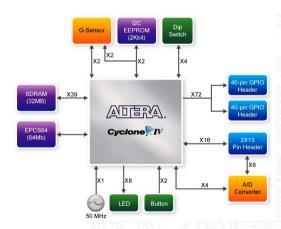

### DEO-Nano (cont.)

Organisation Motivation Systemrealisierung weiteres Vorgeher

- Ein-/Ausgabe

- 8 LEDs

- 2 Taster

- 4 DIP Schalter

- Beschleunigungssensor: ADXL 345, 3-Achsen, 13-bit Auflösung

- A/D Wandler: ADC128S022, 8-Kanal, 12-bit Auflösung

- Erweiterungsstecker

- ullet 2 × 40-Pin: 72 I/O Pins + Spannungsversorgung; 5V, 3,3V, Gnd

- 26-Pin: 16 I/O Pins + 8 analoge Eingänge

- z.B. Verbindung zu (Character-) Display

- vordefinierte IP-Schnittstelle: cDisp14x6

- 14 × 6 Zeichen

## DEO-Nano (cont.)

Systemrealisierung FPGA Serial Configuration Device (EPCS) 32 MB 8 Green LEDs 40-pin GPIO Header SDRAM 2 Push-buttons USB Type mini-AB Port Altera Cyclone IV EP4CE22F17C6N ANTERA. **FPGA** 26-pin Header 2Kb I2C EEPROM 4 Dip Switches A/D Converter 40-pin GPIO Header 2-pin External Digital 50MHz Clock Power Header Accelerometer Oscillator

Organisation Motivation Systemrealisierung weiteres Vorgehe

2X13 Pin

Header

#### **Ablauf**

Organisation Motivation Systemrealisierung **weiteres Vorgehe**n

- Grundlagenvermittlung / Vorlesung

- 1. Festlegung der ISA

- 2.a Hardwareentwurf

- 2.b Softwareentwurf

- Koordination

- Diskussion der Ergebnisse

- ⇒ Projektbericht als Abschluss

Plenum

Plenum Kleingruppen

Kleingruppen

Plenum

Plenum

## Terminplanung

ganisation Motiv

systemrealisierung

weiteres Vorgehen

- 16.10. Vorbereitung (Hausarbeit)

- 23.10. "Rechnerarchitektur: ISA / Pipelining / Speicher" "VHDL-Einführung / HDL-Übersicht"

- 30.10. Projektvorstellung, Fragen

- + praktische Vorführung: VHDL-Simulation, FPGA-Entwurf

- 06.11. Bildung der Arbeitsgruppen / Festlegung der ISA...

..