# Aufgabenblatt 9 Ausgabe: 06.12., Abgabe: 13.12. 12:00

| Gruppe  |                   |

|---------|-------------------|

| Name(n) | Matrikelnummer(n) |

|         |                   |

|         |                   |

|         |                   |

|         |                   |

## **Aufgabe 9.1** (Punkte 10+10+10)

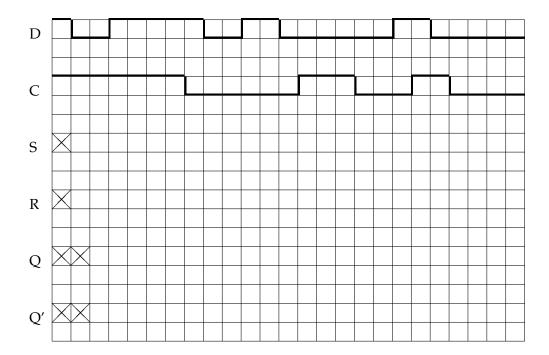

Analyse einer Schaltung: Analysieren Sie die folgende Schaltung aus OR-, AND-, XOR und NAND-Gattern:

- (a) Ermitteln Sie den Ausgangswert y der Funktion für alle Belegungen der Variablen ( $x_3$ ,  $x_2$ ,  $x_1$ ,  $x_0$ ) und erstellen Sie das zugehörige KV-Diagramm.

- (b) Bestimmen Sie aus dem KV-Diagramm die disjunktive Minimalform der Funktion, indem Sie Schleifen einzeichnen.

- (c) Zeichnen Sie das zugehörige Schaltnetz zu (b).

#### **Aufgabe 9.2** (Punkte 15+15+5)

*Minimalformen*: Sei f(a,b,c,d) eine boolsche Funktion und DMF(f) bzw. KMF(f) die disjunktive bzw. die konjunktive Minimalform von f, die man erhält, wenn man f in ein KV-Diagramm einträgt und dann nach den aus der Vorlesung bekannten Verfahren (ohne weitere algebraische Umformungen!) minimiert.

- (a) Geben Sie eine Funktion f(a,b,c,d) mit möglichst vielen UND/ODER-Termen an, für die gilt DMF(f)= KMF(f).

- (b) Wie lassen sich die Funktionen, für die gilt DMF(f)= KMF(f), charakterisieren?

- (c) Welche dieser Funktionen führen zu einer besonders einfachen Reed-Muller-Form?

**Hinweis:** Die KMF(f) hat die allgemeine Form  $k_1(a,b,c,d) \wedge ... \wedge k_n(a,b,c,d)$ , wobei die  $k_i$  boolsche Funktionen sind, in denen (neben Negationen) nur ODER auftreten. Für die DMF(f) erhält man eine ähnliche allgemeine Form. Dann kann man sich überlegen, was DMF(f)= KMF(f) (ohne algebraische Umformungen!) bedeutet.

### Aufgabe 9.3 (Punkte 20)

2:1-Multiplexer: Wir betrachten den 2:1-Multiplexer mit Steuereingang s und Dateneingängen  $a_1$  und  $a_0$ , also  $MUX(s, a_1, a_0) = (s a_1) \lor (\bar{s} a_0)$ .

Geben Sie eine Schaltung nur aus (mehreren) 2:1 Multiplexern an, die einen 1-bit Volladdierer mit den Eingängen a, b und Carry-in  $c_i$ , sowie den beiden Ausgängen s für Summe und  $c_o$  für Carry-out realisiert. Wir nehmen dazu an, dass die Variablen sowohl direkt als auch invertiert zur Verfügung stehen (z.B. a und  $\overline{a}$ ).

Zeichnen Sie ein (Hades-) Schaltbild.

#### Aufgabe 9.4 (Punkte 15)

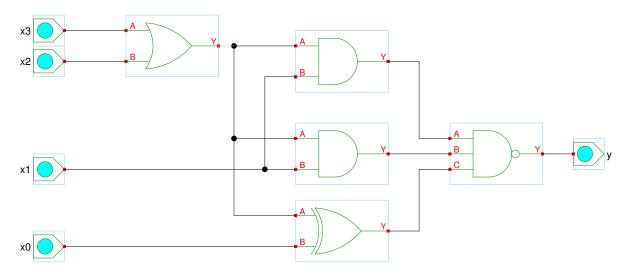

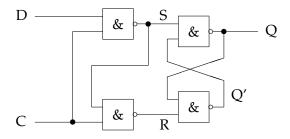

Zeitverhalten von Schaltungen:

Wir untersuchen das Zeitverhalten der folgenden Schaltung mit den beiden Eingängen D und C und den zwei Ausgängen Q und Q'.

Die Signalverzögerungszeit jedes NAND-Gatters genau 15ns ist (ein Teilstrich in folgendem Diagramm). Überlegen Sie sich für den gegebenen Verlauf von D und C den Verlauf von S,

R, Q, Q'. Beachten Sie dabei, dass wegen der Verzögerung S und R im ersten Kästchen Q und Q' in der ersten beiden Kästchen (und möglicherweise auch noch länger undefiniert) sind. Beachten Sie dabei, dass für undefinierte Werte x gelten soll  $\overline{0 \wedge x} = 1$  und  $\overline{1 \wedge x} = x$ :