## 64-040 Modul IP7: Rechnerstrukturen

http://tams.informatik.uni-hamburg.de/ lectures/2011ws/vorlesung/rs

#### Andreas Mäder

Universität Hamburg Fakultät für Mathematik, Informatik und Naturwissenschaften Fachbereich Informatik

Technische Aspekte Multimodaler Systeme

Wintersemester 2011/2012

A. Mäde

64-040 Rechnerstrukturen

# Gliederung (cont.)

Universität Hamburg

- 14. Schaltwerke

- 15. Grundkomponenten für Rechensysteme

- 16. VLSI-Entwurf und -Technologie

- 17. Rechnerarchitektur

- 18. Instruction Set Architecture

- 19. Assembler-Programmierung

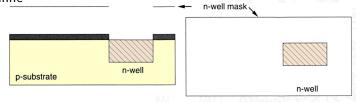

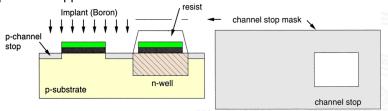

- 20. Computerarchitektur

- 21. Speicherhierarchie

54-040 Rechnerstrukturen

# Gliederung

- 1. Einführung

- 2. Digitalrechner

- 3. Moore's Law

- 4. Information

- 5. Zahldarstellung

- 6. Arithmetik

- 7. Textcodierung

- 8. Boole'sche Algebra

- 9. Logische Operationen

- 10. Codierung

- 11. Schaltfunktionen

- 12. Schaltnetze

- 13. Zeitverhalten

. . . .

64-040 Rechnerstrukturen

# Gliederung

1. Einführung

Universität Hamburg

- 2. Digitalrechne

- 3. Moore's Law

- 4. Information

- 5. Zahldarstellung

- 6. Arithmetil

- 7. Textcodierung

- 8. Boole'sche Algebra

- 9. Logische Operationen

- 10. Codierung

- 11. Schaltfunktionen

- 12. Schaltnetze

- 13. Zeitverhalten

Universität Hamb

MIN-Fakultät Fachbereich Informatik

# Gliederung (cont.)

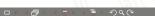

- 14. Schaltwerke

- 15. Grundkomponenten für Rechensysteme

- 16. VLSI-Entwurf und -Technologie

- Rechnerarchitektur

- 18. Instruction Set Architecture

- 19. Assembler-Programmierung

- 20. Computerarchitektur

- 21. Speicherhierarchie

64-040 Rechnerstrukturer

# Motivation

- ► Wie funktioniert ein Digitalrechner?

- ► Mikroprozessoren?

Warum ist das überhaupt wichtig?

- ► Informatik ohne Digitalrechner undenkbar

- ► Grundverständnis der Interaktion von SW und HW

- ► zum Beispiel für "performante" Software

- ► Variantenvielfalt von Mikroprozessorsystemen

- ▶ Supercomputer, Server, Workstations, PCs, . . .

- ▶ Medienverarbeitung, Mobile Geräte, ...

- ► RFID-Tags, Wegwerfcomputer, . . .

- ▶ Bewertung von Trends und Perspektiven

# Inhalt und Lernziele

- ▶ Wie funktioniert ein Digitalrechner?

- ► Warum Mikroprozessoren?

#### Kennenlernen der Themen:

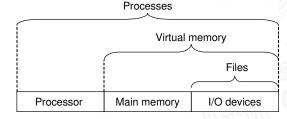

- ► Prinzip des von-Neumann-Rechners

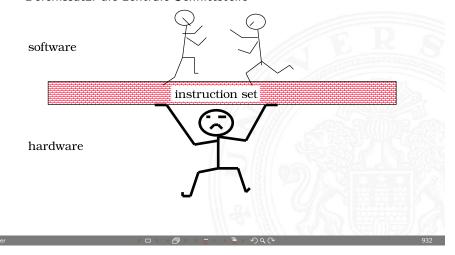

- ► Abstraktionsebenen, Hardware/Software-Schnittstelle

- ► Rechnerarithmetik, Zahldarstellung, Codierung

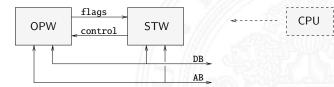

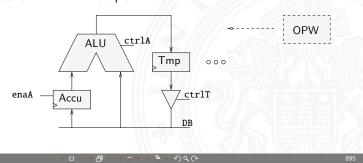

- ► Prozessor mit Steuerwerk und Operationswerk

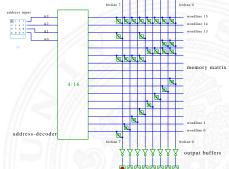

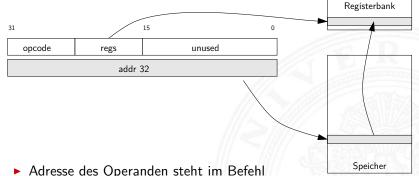

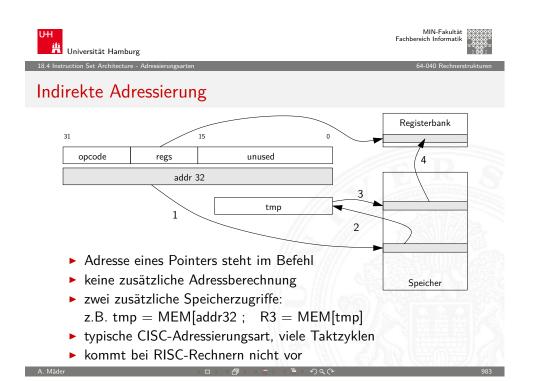

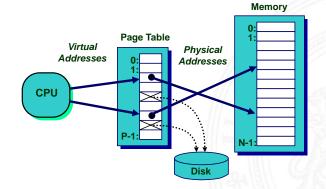

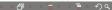

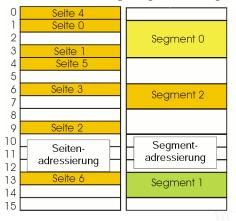

- ► Speicher und -ansteuerung, Adressierungsarten

- ► Befehlssätze, Maschinenprogrammierung

- ► Assemblerprogrammierung, Speicherverwaltung

- ► Fähigkeit zum Einschätzen zukünftiger Entwicklungen

- ► Chancen und Grenzen der Miniaturisierung

64-040 Rechnerstrukturen

# Motivation

- ▶ ständige Fortschritte in Mikroelektronik und Optoelektronik

- ▶ und zwar weiterhin exponentielles Wachstum (50 %...100 % pro Jahr)

- ► Rechenleistung von Prozessoren ("Performance")

- Speicherkapazität (DRAM, SRAM, FLASH)

- Speicherkapazität (Festplatten)

- Bandbreite (Netzwerke)

- ständig neue Möglichkeiten und Anwendungen

- ständig neue Produkte und Techniken

- und ganz gewiss kein "stationärer Zustand"

- ► Roadmaps derzeit bis über 2020 hinaus...

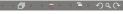

# Technologie-Fortschritt

- ▶ exponentielles Wachstum, typisch 50 % pro Jahr

- ▶ ständig neue Möglichkeiten und Anwendungsfelder

- ▶ ständig neue Produkte und Techniken

- ► Details zu Rechnerorganisation veralten schnell

- ▶ aber die Konzepte bleiben gültig (!)

- ► Schwerpunkt der Vorlesung auf dem "Warum"

- ▶ bitte ein Gefühl für Größenordnungen entwickeln

- ► Software entwickelt sich teilweise viel langsamer

- ▶ LISP seit 1958, Prolog 1972, Smalltalk/OO 1972, usw.

. Mäder

1 Finführung

64-040 Rechnerstrukture

# Neue Anwendungsfelder: Beispiel ReBirth

Propellerheads ReBirth 1996, www.rebirthmuseum.com

► Techno per Software: Echtzeit-Software-Emulation der legendären Roland Synthesizer TB-303 TR-808 TR-909 auf einem PC

64-040 Rechnerstrukturen

# Technologie-Fortschritt: neue Anwendungsfelder

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukti

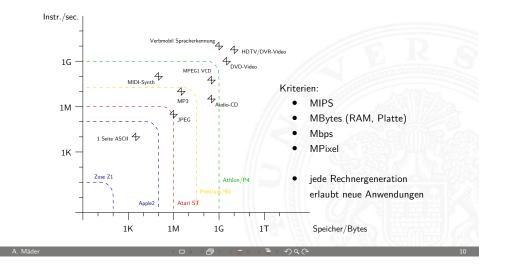

# Neue Anwendungsfelder: Beispiel Autotune

Sie sehen gut aus, aber Ihr Gesang ist lausig?

64-040 Rechnerstrukturen

#### Themen heute

- ► Geschichte der Datenverarbeitung

- ► Wichtige Beispiele

- ► Technologie-Fortschritt, Skalierung

- ► Moore's Gesetz, ITRS-Roadmap

- ► Grenzen der Miniaturisierung: Smart-Dust

- ► Grundprinzip des von-Neumann-Rechners

- ► Aufbau, Befehlszyklus, Befehlssatz

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturer

# Gliederung (cont.)

- 8. Boole'sche Algebra

- Logische Operationen

- 10. Codierung

- 11. Schaltfunktionen

- 12. Schaltnetze

- 13. Zeitverhalten

- Schaltwerke

- 15. Grundkomponenten für Rechensysteme

- 16. VLSI-Entwurf und -Technologie

- 17. Rechnerarchitektur

- Instruction Set Architecture

- 19. Assembler-Programmierung

- Computerarchitektur

MIN-Fakultät Fachbereich Informatik

Gliederung

1. Einführung

2. Digitalrechner

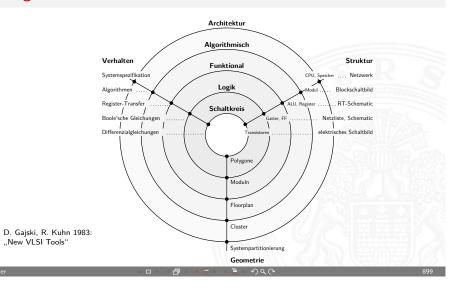

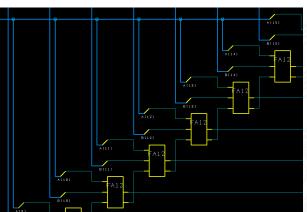

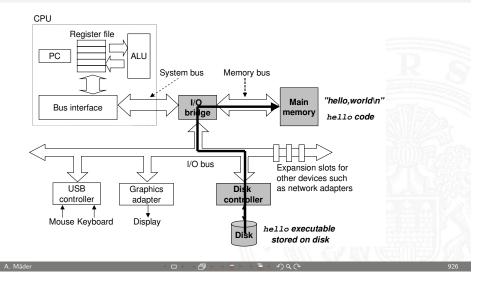

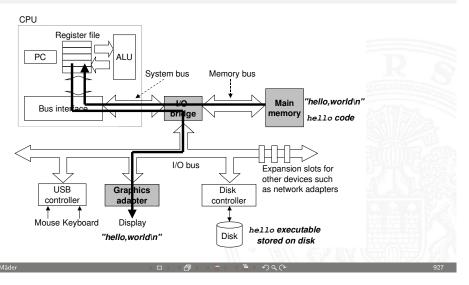

Semantic Gap Abstraktionsebenen

Virtuelle Maschine Beispiel: HelloWorld

von-Neumann-Konzept

Geschichte

- 3. Moore's Law

- 4. Information

- 5. Zahldarstellung

- 6. Arithmetik

- 7. Textcodierung

MIN-Fakultät Fachbereich Informatik

2 Digitalrechner

64-040 Rechnerstrukturen

# Gliederung (cont.)

Universität Hamburg

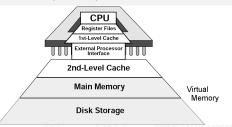

21. Speicherhierarchie

# Definition: Digitalrechner

#### Tanenbaum: Structured Computer Organization

A digital computer is a machine that can solve problems for people by carrying out instructions given to it. A sequence of instructions describing how to perform a certain task is called a program. The electronic circuits of each computer can recognize and directly execute a limited set of simple instructions into which all its programs must be converted before they can be executed.

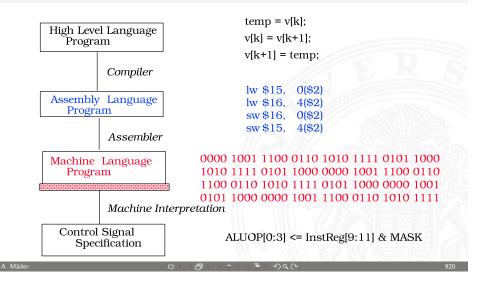

- ▶ Probleme lösen: durch Abarbeiten einfacher **Befehle**

- ► Abfolge solcher Befehle ist ein **Programm**

- ▶ Maschine versteht nur ihre eigene Maschinensprache

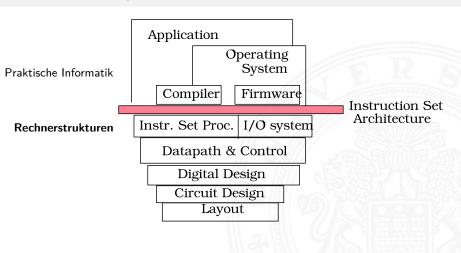

# Rechnerarchitektur bzw. -organisation

- ▶ Definition solcher Abstraktionsebenen bzw. Schichten

- ▶ mit möglichst einfachen und sauberen Schnittstellen

- ▶ jede Ebene definiert eine neue (mächtigere) **Sprache**

- diverse Optimierungs-Kriterien/Möglichkeiten:

- ▶ Performance, Hardwarekosten, Softwarekosten, . . .

- ▶ Wartungsfreundlichkeit, Stromverbrauch, ...

### Achtung / Vorsicht:

- ► Gesamtverständnis erfordert Kenntnisse auf allen Ebenen

- ▶ häufig Rückwirkung von unteren auf obere Ebenen

# Befehlssatz und Semantic Gap

• ... directly execute a limited set of simple instructions...

Typische Beispiele für solche Befehle:

- ▶ addiere die zwei Zahlen in Register R1 und R2

- ▶ überprüfe, ob das Resultat Null ist

- ▶ kopiere ein Datenwort von Adresse 13 ins Register R4

- ⇒ extrem niedriges Abstraktionsniveau

- ► natürliche Sprache mit Kontextwissen Beispiel: "vereinbaren Sie einen Termin mit dem Steuerberater"

- ▶ **Semantic gap**: Diskrepanz zu einfachen/elementaren Anweisungen

- ▶ Vermittlung zwischen Mensch und Computer erfordert zusätzliche Abstraktionsebenen und Software

# Rückwirkung von unteren Ebenen: Arithmetik

```

public class Overflow {

public static void main( String[] args ) {

printInt( 0 );

printInt( 1 );

printInt( -1 );

// -1

// 14

printInt(2+(3*4));

printInt( 100*200*300 );

// 6000000

printInt( 100*200*300*400 );

// -1894967296

(!)

printDouble( 1.0 );

// 1.0

// 0.3

printDouble( 0.3 );

printDouble( 0.1 + 0.1 + 0.1 ); // 0.3000000000000004 (!)

printDouble( (0.3) - (0.1+0.1+0.1) ); // -5.5E-17

(!)

```

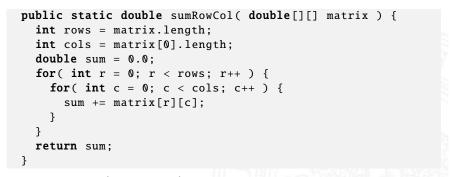

# Rückwirkung von unteren Ebenen: Performance

$\begin{array}{lll} \text{Matrix creation (5000} \times 5000) & 2105 \text{ msec.} \\ \text{Matrix row-col summation} & 75 \text{ msec.} \\ \text{Matrix col-row summation} & 383 \text{ msec.} & \Rightarrow 5x \text{ langsamer} \\ \text{Sum} = 600.8473695346258 \ / \ 600.8473695342268} & \Rightarrow \text{andere Werte} \\ \end{array}$

UH

Universität Hamburg

MIN-Fakultät Fachbereich Informatik

2.2 Digitalrechner - Abstraktionsebener

64-040 Rechnerstrukturer

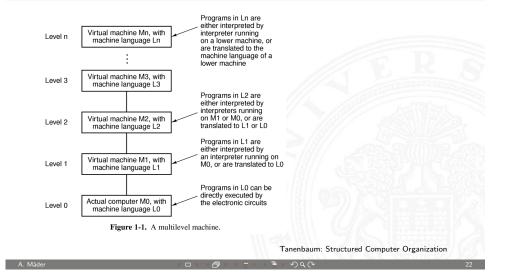

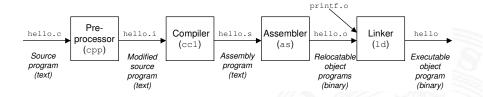

# Abstraktionsebenen und Sprachen

- ▶ jede Ebene definiert eine neue (mächtigere) Sprache

- ► Abstraktionsebene Sprache

- ▶ L0 < L1 < L2 < L3 < ...

Software zur Übersetzung zwischen den Ebenen

► Compiler:

Erzeugen eines neuen Programms, in dem jeder L1 Befehl durch eine zugehörige Folge von L0 Befehlen ersetzt wird

► Interpreter: direkte Ausführung der L0 Befehlsfolgen zu jedem L1 Befehl

MIN-Fakultät Fachbereich Informatik

- Abstraktionsebenen 64-040 Rec

#### Maschine mit mehreren Ebenen

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukture

Virtuelle Maschine

# ► für einen Interpreter sind L1 Befehle einfach nur Daten

- die dann in die zugehörigen LO Befehle umgesetzt werden

# ⇒ dies ist gleichwertig mit einer:

# Virtuellen Maschine M1 für die Sprache L1

- ▶ ein Interpreter erlaubt es, jede beliebige Maschine zu simulieren

- ▶ und zwar auf jeder beliebigen (einfacheren) Maschine M0

- ▶ Programmierer muss sich nicht um untere Schichten kümmern

- ► Nachteil: die virtuelle Maschine ist meistens langsamer als die echte Maschine M1

- ► Maschine M0 kann wiederum eine virtuelle Maschine sein (!)

- unterste Schicht ist jeweils die Hardware

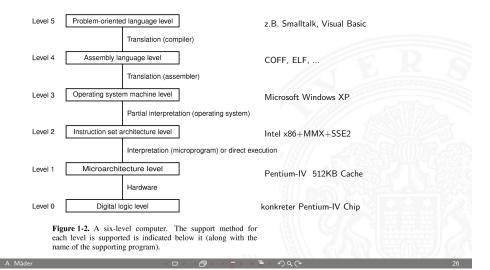

# Übliche Einteilung der Ebenen

Anwendungsebene Hochsprachen (Java, Smalltalk, ...)

Assemblerebene low-level Anwendungsprogrammierung

Betriebssystemebene Betriebssystem, Systemprogrammierung

Rechnerarchitektur Schnittstelle zwischen SW und HW,

Befehlssatz, Datentypen

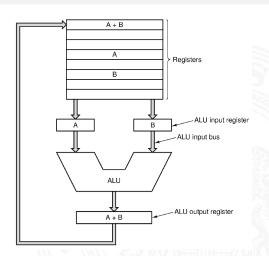

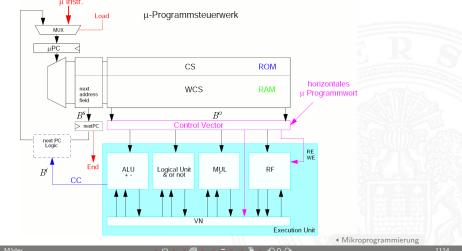

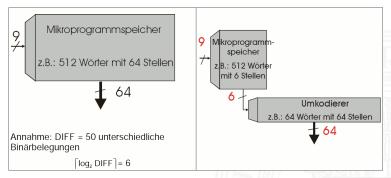

Mikroarchitektur Steuerwerk und Operationswerk:

Register, ALU, Speicher, ...

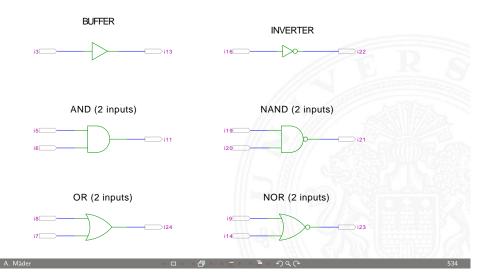

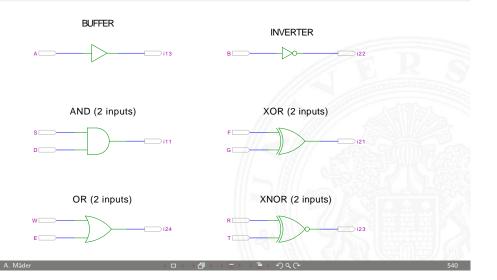

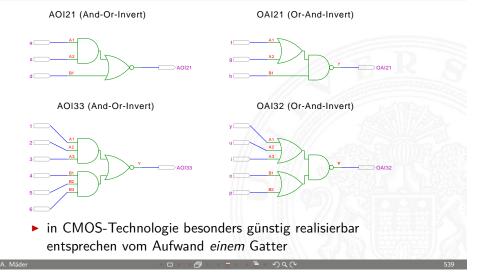

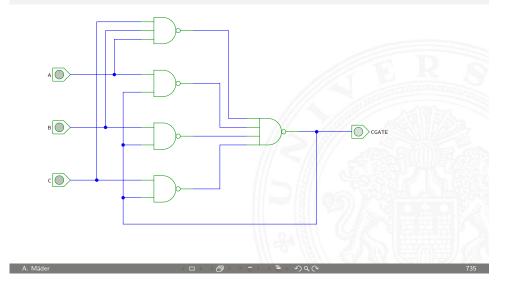

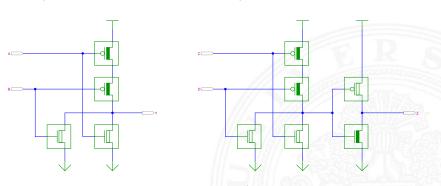

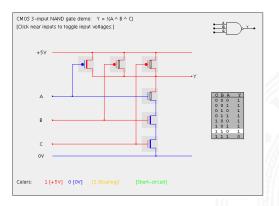

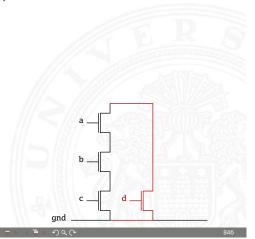

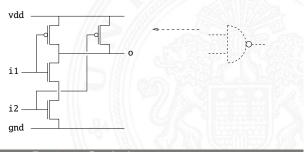

Logikebene Grundschaltungen: Gatter, Flipflops, ...

Transistorebene Transistoren, Chip-Layout

Physikalische Ebene Elektrotechnik, Geometrien

A Måder □ 📵 - 😩 🗸 Q 🤃 ?5

MIN-Fakultät Fachbereich Informatik

2 3 Digitalrechner - Virtuelle Maschine

64-040 Rechnerstrukturer

# Hinweis: Ebenen vs. Vorlesungen im BSc-Studiengang

Anwendungsebene: SE1..SE3, AD, ...

Assemblerebene: RS Betriebssystemebene: GSS

Rechnerarchitektur: RS, RAM

Mikroarchitektur: RS, RAM

Logikebene: RS, RAM

Device-Level: RAM

MIN-Fakultät Fachbereich Informatik

2.3 Digitalrechner - Virtuelle Maschin

-040 Rechnerstrukturen

# Beispiel: Sechs Ebenen

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

# HelloWorld: Anwendungsebene: Quellcode

```

/* HelloWorld.c - print a welcome message */

#include <stdio.h>

int main( int argc, char ** argv ) {

printf( "Hello, world!\n" );

return 0;

}

```

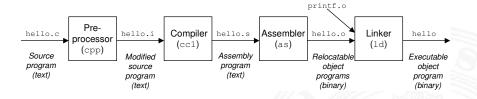

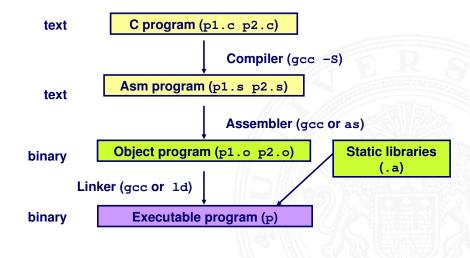

#### Übersetzung

```

gcc -S HelloWorld.c

gcc -c HelloWorld.c

gcc -o HelloWorld.exe HelloWorld.c

```

Universität Hamburg

MIN-Fakultät Fachbereich Informatik

# HelloWorld: Assemblerebene: cat HelloWorld.s

```

main:

4(%esp), %ecx

andl $-16, %esp

pushl -4(\%ecx)

pushl %ebp

%esp, %ebp

pushl %ecx

$4, %esp

$.LC0, (%esp)

movl

call

puts

$0, %eax

movl

addl

$4, %esp

%ecx

popl

popl

%ebp

-4(%ecx), %esp

ret

```

MIN-Fakultät

# HelloWorld: Disassemblieren: objdump -d HelloWorld.o

```

HelloWorld.o:

file format elf32-i386

Disassembly of section .text:

00000000 <main>:

8d 4c 24 04

lea

0x4(%esp),%ecx

83 e4 f0

and

$0xfffffff0,%esp

ff 71 fc

pushl

0xfffffffc(%ecx)

a:

55

push

%ebp

89 e5

b:

mov

%esp,%ebp

d:

51

%ecx

push

e:

83 ec 04

sub

$0x4.%esp

11:

c7 04 24 00 00 00 00

movl

$0x0,(%esp)

18:

e8 fc ff ff ff

call

19 < main + 0x19 >

1d:

b8 00 00 00 00

mov

$0x0,%eax

22:

83 c4 04

$0x4,%esp

add

```

# HelloWorld: Objectcode: od -x HelloWorld.o

```

0000000 457f 464c 0101 0001 0000 0000 0000 0000

0000060 000b 0008 4c8d 0424 e483 fff0 fc71 8955

0000100 51e5 ec83 c704 2404 0000 0000 fce8 ffff

0000120 b8ff 0000 0000 c483 5904 8d5d fc61 00c3

0000140 6548 6c6c 2c6f 7720 726f 646c 0021 4700

0000160 4343 203a 4728 554e 2029 2e34 2e31 2032

0000200 3032 3630 3131 3531 2820 7270 7265 6c65

0000220 6165 6573 2029 5328 5355 2045 694c 756e

0000240 2978 0000 732e 6d79 6174 0062 732e 7274

0000260 6174 0062 732e 7368 7274 6174 0062 722e

0000300 6c65 742e 7865 0074 642e 7461 0061 622e

0000320 7373 2e00 6f72 6164 6174 2e00 6f63 6d6d

0000340 6e65 0074 6e2e 746f 2e65 4e47 2d55 7473

```

MIN-Fakultät

# HelloWorld: Maschinencode: od -x HelloWorld.exe

```

0000000 457f 464c 0101 0001 0000 0000 0000 0000

0000020 0002 0003 0001 0000 8310 0804 0034 0000

0000040 126c 0000 0000 0000 0034 0020 0009 0028

0000060 001c 001b 0006 0000 0034 0000 8034 0804

0000100 8034 0804 0120 0000 0120 0000 0005 0000

0000120 0004 0000 0003 0000 0154 0000 8154 0804

0000140 8154 0804 0013 0000 0013 0000 0004 0000

0000160 0001 0000 0001 0000 0000 0000 8000 0804

0000200 8000 0804 04c4 0000 04c4 0000 0005 0000

0000220 1000 0000 0001 0000 0f14 0000 9f14 0804

0000240 9f14 0804 0104 0000 0108 0000 0006 0000

0000260 1000 0000 0002 0000 0f28 0000 9f28 0804

```

# Hardware: "Versteinerte Software"

- eine virtuelle Maschine führt L1 Software aus

- und wird mit Software oder Hardware realisiert

- ⇒ Software und Hardware sind logisch äquivalent "Hardware is just petrified Software"

(K.P.Lentz)

— jedenfalls in Bezug auf L1 Programmausführung

Entscheidung für Software- oder Hardwarerealisierung?

- ▶ abhängig von vielen Faktoren, u.a.

- ► Kosten, Performance, Zuverlässigkeit

- ► Anzahl der (vermuteten) Änderungen und Updates

- ► Sicherheit gegen Kopieren, ...

MIN-Fakultät Fachbereich Informatik

2.5 Digitalrechner - von-Neumann-Konzep

64-040 Rechnerstrukturen

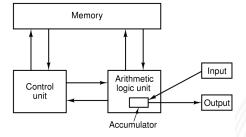

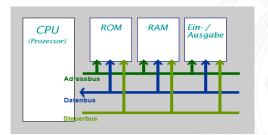

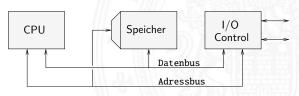

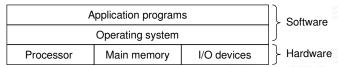

# von-Neumann Rechner

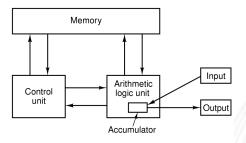

Figure 1-5. The original von Neumann machine.

### Fünf zentrale Komponenten:

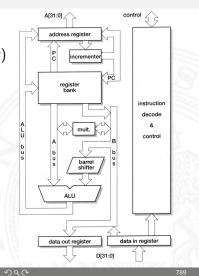

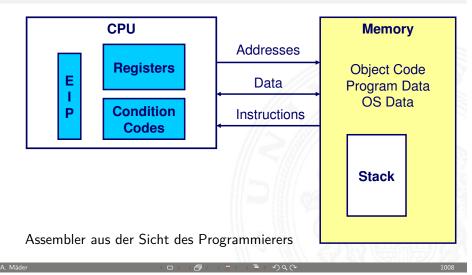

- Prozessor mit Steuerwerk und Rechenwerk (ALU, Register)

- ▶ **Speicher**, gemeinsam genutzt für Programme und Daten

- ► Eingabe- und Ausgabewerke

MIN-Fakultät Fachbereich Informatik

2.5 Digitalrechner - von-Neumann-Konzept

4-040 Rechnerstrukturen

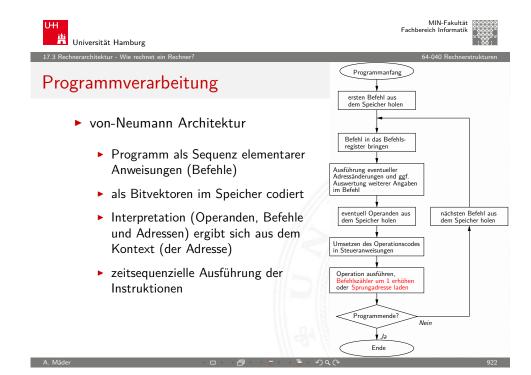

# von-Neumann-Konzept

- ▶ J. Mauchly, J.P. Eckert, J. von-Neumann 1945

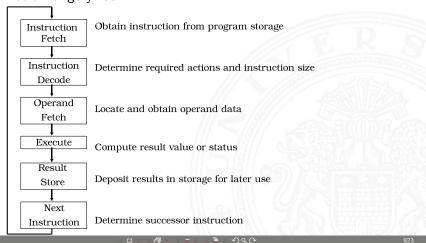

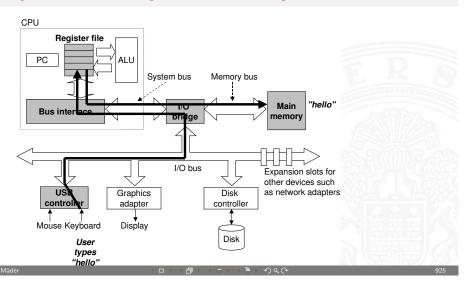

- ▶ System mit Prozessor, Speicher, Peripheriegeräten

- ▶ gemeinsamer Speicher für Programme und Daten

- ▶ Programme können wie Daten manipuliert werden

- ▶ Daten können als Programm ausgeführt werden

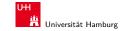

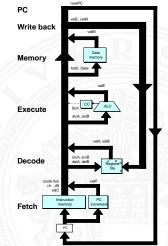

- ► Befehlszyklus: Befehl holen, decodieren, ausführen

- enorm flexibel

- ▶ alle aktuellen Rechner basieren auf diesem Prinzip

- ▶ aber vielfältige Architekturvarianten, Befehlssätze, usw.

A. Mäder

> 《聞 > 《三》《喜》���

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukture

# von-Neumann Rechner (cont.)

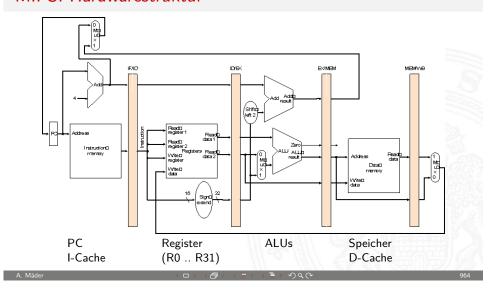

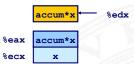

- ► Steuerwerk: zwei zentrale Register

- ▶ Befehlszähler (program counter PC)

- ▶ Befehlsregister (instruction register IR)

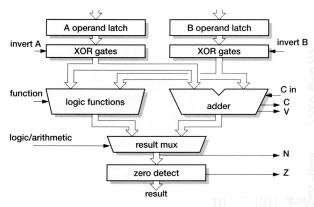

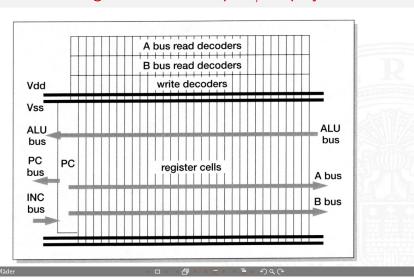

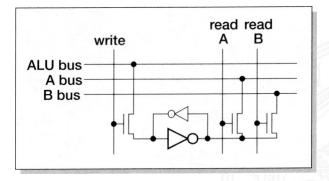

- ► Operationswerk (Datenpfad, *data-path*)

- ► Rechenwerk (arithmetic-logic unit ALU)

- Universalregister (mindestens 1 Akkumulator, typisch 8..64 Register)

- ▶ evtl. Register mit Spezialaufgaben

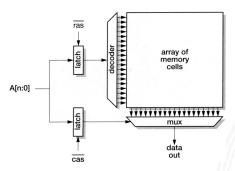

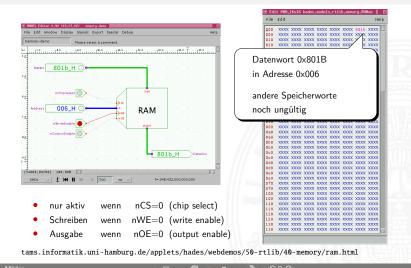

- ► Speicher (*memory*)

- ► Hauptspeicher/RAM: random-access memory

- ► Hauptspeicher/ROM: read-only memory zum Booten

- ► Externspeicher: Festplatten, CD/DVD, Magnetbänder

- Peripheriegeräte (Eingabe/Ausgabe, I/O)

2.5 Digitalrechner - von-Neumann-Konzept

4-040 Rechnerstrukturen

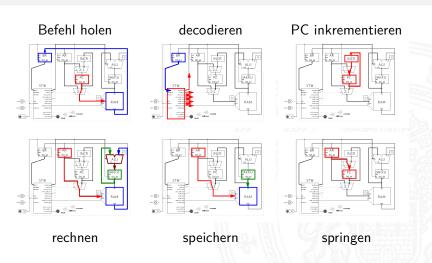

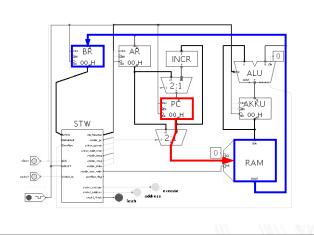

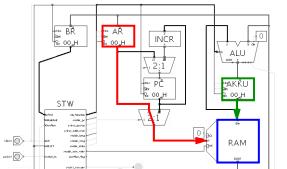

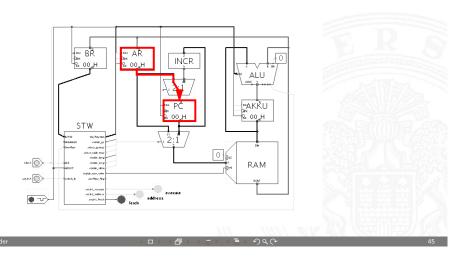

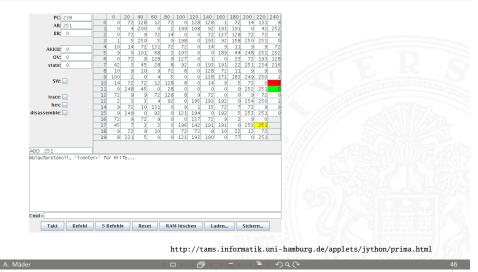

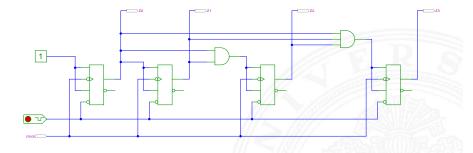

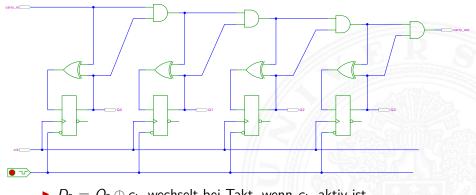

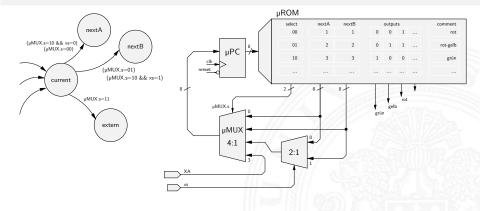

# PRIMA: die Primitive Maschine

ein (minimaler) 8-bit von-Neumann Rechner

- ▶ RAM: Hauptspeicher 256 Worte à 8-bit

- ▶ vier 8-bit Register:

- ► PC: program-counter

- ▶ BR: instruction register ("Befehlsregister")

- ► AR: address register (Speicheradressen und Sprungbefehle)

- ► AKKU: accumulator (arithmetische Operationen)

- eine ALU für Addition, Inkrement, Shift-Operationen

- ▶ ein Schalter als Eingabegerät

- ► sehr einfacher Befehlssatz

- ▶ Demo: http://tams.informatik.uni-hamburg.de/applets/ hades/webdemos/50-rtlib/90-prima/chapter.html

STW

STW

STW

STW

STW

STW

ARRU

PRIMA: die Primitive Maschine

http://tams.informatik.uni-hamburg.de/applets/hades/webdemos/50-rtlib/90-prima/chapter.html

3

MIN-Fakultät Fachbereich Informatik

2.5 Digitalrechner - von-Neumann-Konzent

64-040 Rechnerstrukturen

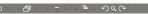

# PRIMA: die Zyklen

# PRIMA: Befehl holen BR = RAM[PC]

64-040 Rechnerstrukturen

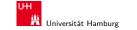

# PRIMA: decodieren

Steuersignale = decode(BR)

MIN-Fakultät Fachbereich Informatik

2.5 Digitalrechner - von-Neumann-Konzent

64-040 Rechnerstrukture

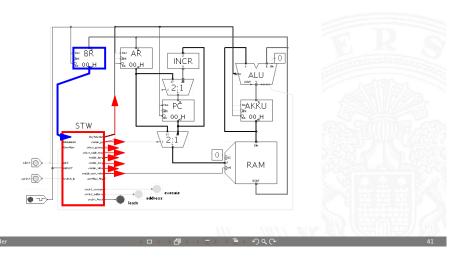

# PRIMA: rechnen

Akku = Akku + RAM[AR]

MIN-Fakultät Fachbereich Informatik

2.5 Digitalrechner - von-Neumann-Konzept

4-040 Rechnerstrukturen

# PRIMA: PC inkrementieren

PC = PC+1

MIN-Fakultät Fachbereich Informatik

5 Digitalrechner - von-Neumann-Konzent

64-040 Rechnerstrukture

# PRIMA: speichern

RAM[AR] = Akku

PRIMA: springen

PC = AR

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

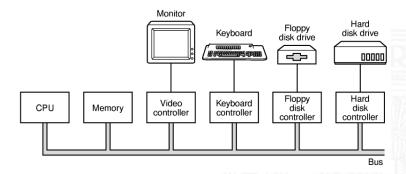

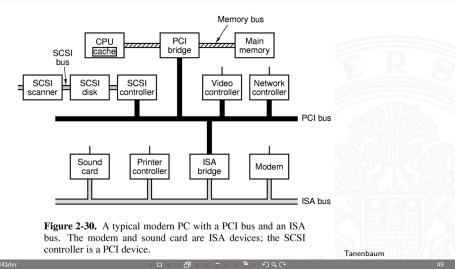

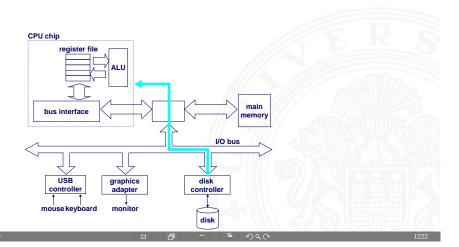

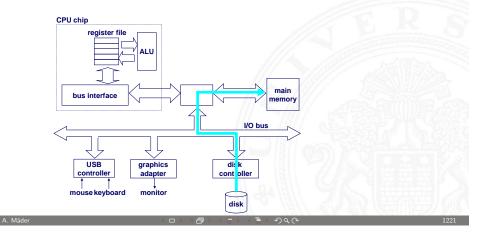

# Personal Computer: Aufbau des IBM PC (1981)

- ► Intel 8086/8088, 512 KByte RAM, Betriebssystem MS-DOS

- ▶ alle Komponenten über den zentralen ("ISA"-) Bus verbunden

- ► Erweiterung über Einsteckkarten

MIN-Fakultät Fachbereich Informatik

2.5 Digitalrechner - von-Neumann-Konzept

4-040 Rechnerstrukturen

# PRIMA: Simulator

MIN-Fakultät Fachbereich Informatik

.5 Digitalrechner - von-Neumann-Konzept

64-040 Rechnerstrukture

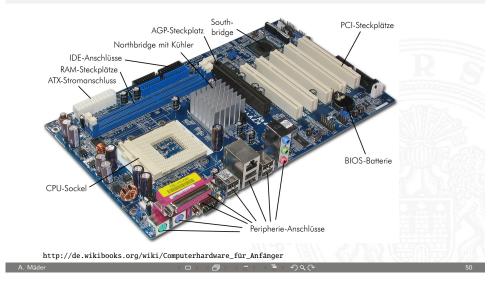

# Personal Computer: Prototyp (1981) und Hauptplatine

Universität Hamburg

# Personal Computer: Aufbau mit PCI-Bus (2000)

Universität Hamburg

MIN-Fakultät

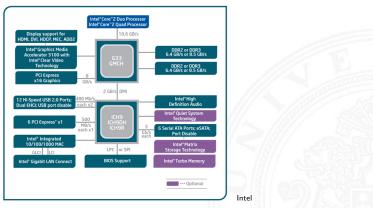

# Personal Computer: Aufbau (2010)

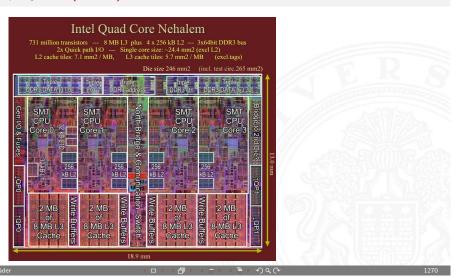

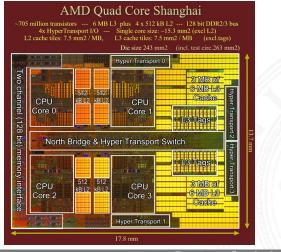

- ► Mehrkern-Prozessoren ("dual-/quad core")

- ▶ schnelle serielle Direktverbindungen statt PCI/ISA Bus

# Personal Computer: Hauptplatine (2005)

MIN-Fakultät

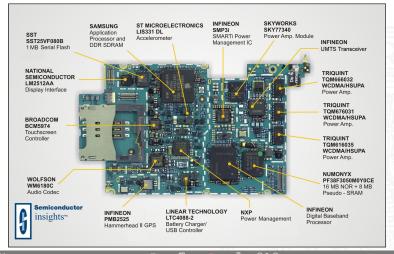

# Mobilgeräte: Smartphone (2010)

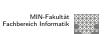

# Timeline: Vorgeschichte

- Abakus als erste Rechenhilfe Pascal: Addierer/Subtrahierer

- Leibniz: Vier-Operationen-Rechenmaschine 1671

- Babbage: Analytical Engine 1837

- Zuse: Z1 (mechanisch) 1937

- Zuse: Z3 (Relais, Gleitkomma) 1939

- Atanasoff & Berry: ABC (Röhren, Magnettrommel) 1941

- Mc-Culloch Pitts (Neuronenmodell) 1944

- 1946 Eckert & Mauchly: ENIAC (Röhren)

- 1949 Eckert, Mauchly, von Neumann: EDVAC

- (erster speicherprogrammierter Rechner)

- 1949 Manchester Mark-1 (Indexregister)

Jniversität Hamburg

# Mechanische Rechenmaschinen

- Schickard: Sprossenrad, Addierer/Subtrahierer 1623

- Pascal: "Pascalene" 1642

- Leibniz: Staffelwalze, Multiplikation/Division 1673

- 1774 Philipp Matthäus Hahn: erste gebrauchsfähige

"4-Spezies"-Maschine

MIN-Fakultät

#### **Abakus**

MIN-Fakultät

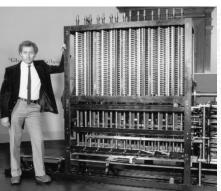

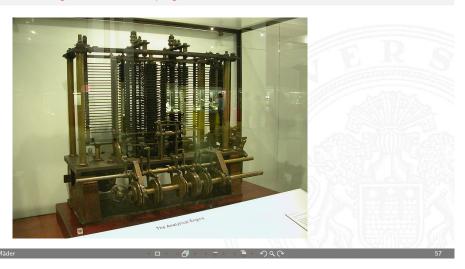

# Difference Engine

Charles Babbage 1822: Berechnung nautischer Tabellen

Original von 1832 und Nachbau von 1989, London Science Museum

# Analytical Engine

Charles Babbage 1837-1871: frei programmierbar, Lochkarten, unvollendet

MIN-Fakultät Fachbereich Informatik

igitalrechner - Geschichte 64-040 Rechnerstri

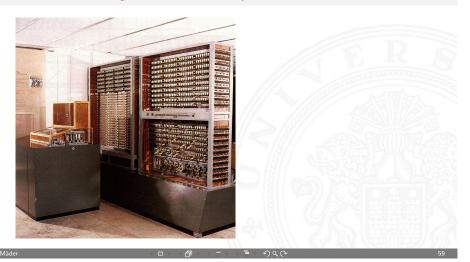

# Zuse Z3

Konrad Zuse 1941, 64 Register, 22-bit, 2000 Relays, Lochfilm

MIN-Fakultät Fachbereich Informatik

2.6 Digitalrechner - Geschichte

04-040 Rechnerstrukturen

# Zuse Z1

Konrad Zuse 1937: 64 Register, 22-bit, mechanisch, Lochfilm

MIN-Fakultät Fachbereich Informatik

Digitalrechner - Geschichte

64-040 Rechnerstrukturen

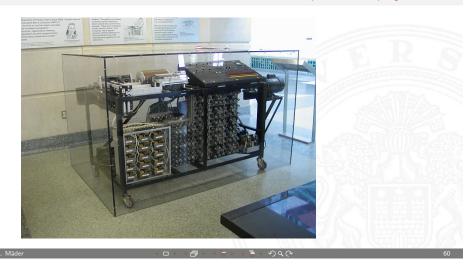

# Atanasoff-Berry Computer (ABC)

J.V.Atanasoff 1942: 50-bit Festkomma, Röhren und Trommelspeicher, fest programmiert

UH

Universität Hamburg

MIN-Fakultät Fachbereich Informatik

Digitalrechner - Geschichte

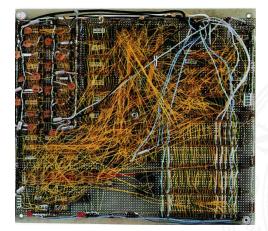

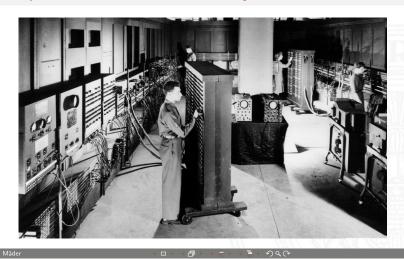

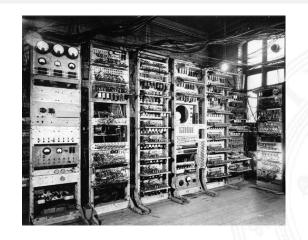

# ENIAC — Electronic Numerical Integrator and Computer

Mauchly & Eckert, 1946: Röhren, Steckbrett-Programm

UH Universität Hamburg MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

# **EDVAC**

Mauchly, Eckert & von Neumann, 1949: Röhren, speicherprogrammiert

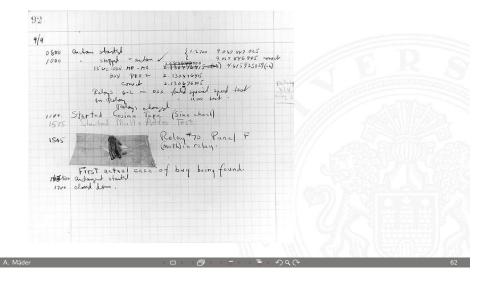

# First computer bug

MIN-Fakultät Fachbereich Informatik

2.6 Digitalrechner - Geschichte

64-040 Rechnerstrukturen

# Manchester Mark-1

Williams & Kilburn, 1949: Trommelspeicher, Indexregister

# Manchester EDSAC

Wilkes 1951: Mikroprogrammierung, Unterprogramme, speicherprogrammiert

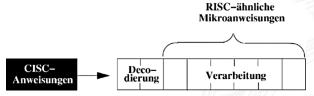

# erste Computer, ca. 1950:

- zunächst noch kaum Softwareunterstützung

- nur zwei Schichten:

- 1. Programmierung in elementarer Maschinensprache (ISA level)

- 2. Hardware in Röhrentechnik (device logic level)

- Hardware kompliziert und unzuverlässig

#### Mikroprogrammierung (Maurice Wilkes, Cambridge, 1951):

- ▶ Programmierung in komfortabler Maschinensprache

- ► Mikroprogramm-Steuerwerk (Interpreter)

- ▶ einfache, zuverlässigere Hardware

- ► Grundidee der sog. CISC-Rechner (68000, 8086, VAX)

MIN-Fakultät

# Timeline: Verbesserungen

(Pipeline) 1952: IBM 701 (Rechnerfamilie, software-kompatibel) 1964: IBM S/360 (4-bit Mikroprozessor) 1971: Intel 4004 (8-bit Mikrocomputer-System) 1972: Intel 8008 (16/32-bit Mikroprozessor) 1979: Motorola 68000 1980: Intel 8087 (Gleitkomma-Koprozessor) 1981: Intel 8088 (8/16-bit für IBM PC) (32-bit, Pipeline, on-chip Cache) 1984: Motorola 68020 1992: DEC Alpha AXP (64-bit RISC-Mikroprozessor) (MultiMedia eXtension Befehlssatz ) 1997: Intel MMX 2006: Sony Playstation 3 (1+8 Kern-Multiprozessor) 2006: Intel-VT / AMD-V (Virtualisierung)

# erste Betriebssysteme

- erste Rechner jeweils nur von einer Person benutzt

- ► Anwender = Programmierer = Operator

- ▶ Programm laden, ausführen, Fehler suchen, usw.

- ⇒ Maschine wird nicht gut ausgelastet

- ⇒ Anwender mit lästigen Details überfordert

#### Einführung von Betriebssystemen

- "system calls"

- ▶ Batch-Modus: Programm abschicken, warten

- ► Resultate am nächsten Tag abholen

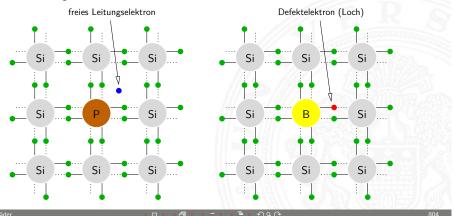

## zweite Generation: Transistoren

- ► Erfindung des Transistors 1948

- J. Bardeen, W. Brattain, W. Shockley

- ▶ schneller, zuverlässiger, sparsamer als Röhren

- ▶ Miniaturisierung und dramatische Kostensenkung

- ▶ Beispiel Digial Equipment Corporation PDP-1 (1961)

- ▶ 4K Speicher (4096 Worte á 18-bit)

- ► 200 kHz Taktfrequenz

- **120.000**\$

- ► Grafikdisplay: erste Computerspiele

- ► Nachfolger PDP-8: 16.000\$

- erstes Bussystem

- ▶ 50.000 Stück verkauft

# dritte Generation: ICs

- ► Erfindung der integrierten Schaltung 1958 (Noyce, Kilby)

- ▶ Dutzende... Hunderte... Tausende Transistoren auf einem Chip

- ▶ IBM Serie-360: viele Maschinen, ein einheitlicher Befehlssatz

- ▶ volle Softwarekompatibilität

| Property                        | Model 30 | Model 40 | Model 50 | Model 65 |

|---------------------------------|----------|----------|----------|----------|

| Relative performance            | 1        | 3.5      | 10       | 21       |

| Cycle time (nsec)               | 1000     | 625      | 500      | 250      |

| Maximum memory (KB)             | 64       | 256      | 256      | 512      |

| Bytes fetched per cycle         | 1        | 2        | 4        | 16       |

| Maximum number of data channels | 3        | 3        | 4        | 6        |

**Figure 1-7.** The initial offering of the IBM 360 product line.

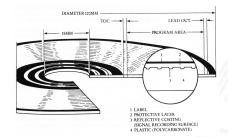

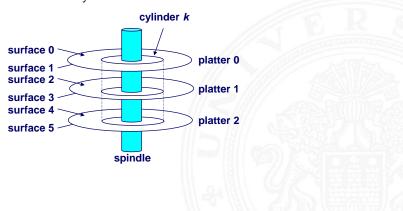

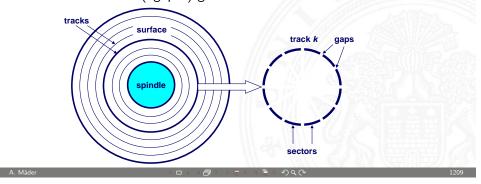

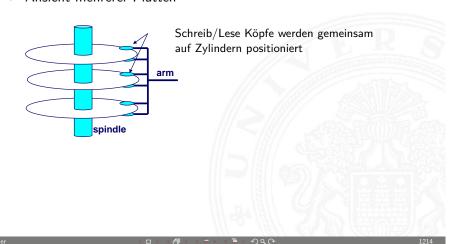

# **Festplatten**

#### Massenspeicher bei frühen Computern:

- ► Lochkarten

- ▶ Lochstreifen

- Magnetband

- Magnettrommel

- ► Festplatte IBM 350 RAMAC (1956) 5 MByte, 600 ms Zugriffszeit

http://de.wikibooks.org/wiki/Computerhardware\_für\_Anfänger

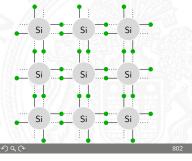

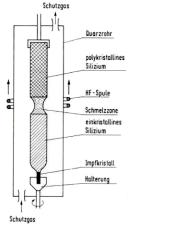

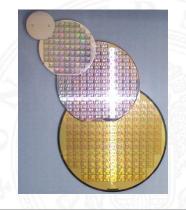

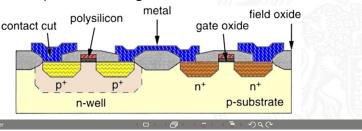

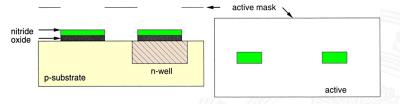

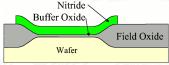

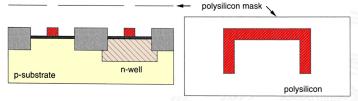

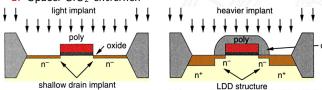

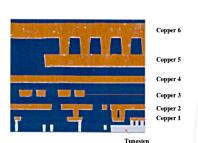

# vierte Generation: VLSI

- ► VLSI = Very Large Scale Integration

- ▶ ab 10.000+ Transistoren pro Chip

- ▶ gesamter Prozessor passt auf einen Chip

- ▶ steigende Integrationsdichte erlaubt immer mehr Funktionen

1972 Intel 4004: erster Mikroprozessor 1975 Intel 8080, Motorola 6800, MOS 6502, ... 1981 IBM PC ("personal computer") mit Intel 8088

- ▶ Massenfertigung erlaubt billige Prozessoren (< 1\$)

- ▶ Miniaturisierung ermöglicht mobile Geräte

64-040 Rechnerstrukturen

# Xerox Alto: first workstation

MIN-Fakultät Fachbereich Informatik

oore's Law 64-040 Rechnerstrukt

# Gliederung

- Einführung

- 2. Digitalrechner

- 3. Moore's Law

System on a chip Smart Dust Roadmap und Grenzen des Wachstums

- 4. Information

- 5. Zahldarstellung

- 6. Arithmetik

- 7. Textcodierung

- 8. Boole'sche Algebra

- 9. Logische Operationen

- 10. Codierung

ner - Geschichte

# Rechner-Spektrum

| Туре                       | Price (\$) | Example application             |

|----------------------------|------------|---------------------------------|

| Disposable computer        | 1          | Greeting cards                  |

| Embedded computer          | 10         | Watches, cars, appliances       |

| Game computer              | 100        | Home video games                |

| Personal computer          | 1K         | Desktop or portable computer    |

| Server                     | 10K        | Network server                  |

| Collection of Workstations | 100K       | Departmental minisupercomputer  |

| Mainframe                  | 1M         | Batch data processing in a bank |

| Supercomputer              | 10M        | Long range weather prediction   |

**Figure 1-9.** The current spectrum of computers available. The prices should be taken with a grain (or better yet, a metric ton) of salt.

# Gliederung (cont.)

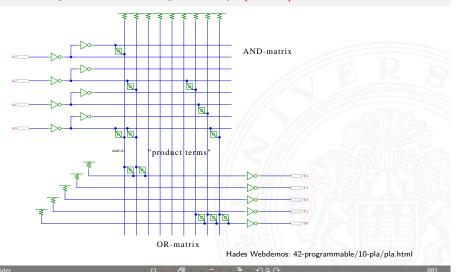

- 11. Schaltfunktionen

- 12. Schaltnetze

- 13 Zoitvorhaltor

- 11 Schaltwork

- 15. Grundkomponenten für Rechensystem

- 16. VLSI-Entwurf und -Technologie

- 17. Rechnerarchitektu

- 18. Instruction Set Architecture

- 19. Assembler-Programmierung

- 20. Computerarchitektu

- 21. Speicherhierarchie

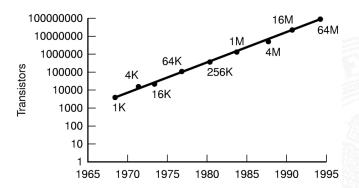

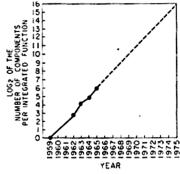

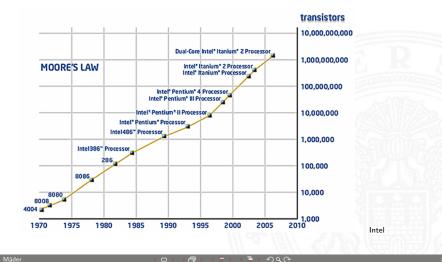

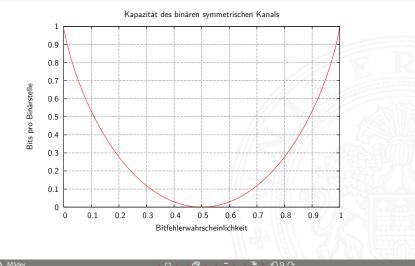

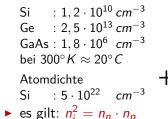

# Moore's Law

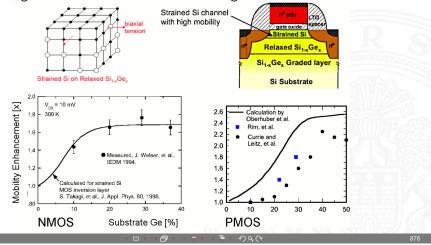

- ▶ bessere Technologie ermöglicht immer kleinere Transistoren

- ► Materialkosten sind proportional zur Chipfläche

- ⇒ bei gleicher Funktion kleinere und billigere Chips

- ⇒ bei gleicher Größe leistungsfähigere Chips

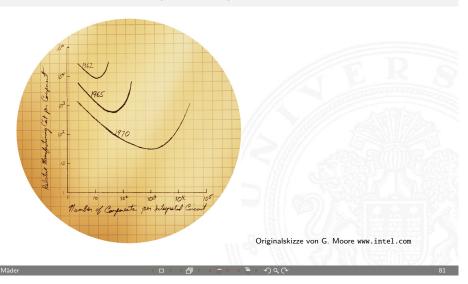

#### Moore's Law

Gordon Moore, Mitgründer von Intel, 1965

Speicherkapazität von ICs vervierfacht sich alle drei Jahre

- ⇒ schnelles exponentielles Wachstum

- ▶ klares Kostenoptimum bei hoher Integrationsdichte

- ▶ trifft auch auf Prozessoren zu

64-040 Rechnerstrukturen

# Moore's Law: Transistoren pro Speicherchip

**Figure 1-8.** Moore's law predicts a 60 percent annual increase in the number of transistors that can be put on a chip. The data points given in this figure are memory sizes, in bits.

MIN-Fakultät Fachbereich Informatik

Moore's Law 64-040 Rechnerstrukture

# Moore's Law (cont.)

Gordon Moore 1965: "Cramming more components onto integrated circuits"

Wird das so weitergehen?

- ► Vorhersage gilt immer noch

- "ITRS" Prognose bis über Jahr 2020 hinaus

Mäder

<=> < => ୬ Q @

UH

Universität Hamburg

64-040 Rechnerstrukturen

# Moore's Law: Evolution des Intel x86 (bis 2010)

# Moore's Law: Kosten pro Komponente

64-040 Rechnerstruk

# Leistungssteigerung der Spitzenrechner seit 1993

| Jahr | Rechner                              | Linpack    | Zahl der      |

|------|--------------------------------------|------------|---------------|

|      |                                      | in Gflop/s | Prozessoren   |

| 1993 | Fujitsu NWT                          | 124        | 140           |

| 1994 | Intel Paragon XP/S MP                | 281        | 6.768         |

| 1996 | Hitachi CP-PACS                      | 368        | 2.048         |

| 1997 | Intel ASCI Red (200 MHz Pentium Pro) | 1.338      | 9.152         |

| 1998 | ASCI Blue-Pacific (IBM SP 640E)      | 2.144      | 5.808         |

| 1999 | ASCI Intel Red (Pentium II Xeon)     | 2.379      | 9.632         |

| 2000 | ASCI White, IBM (SP Power 3)         | 4.903      | 7.424         |

| 2002 | Earth Simulator, NEC                 | 35.610     | 5.104         |

| 2006 | JUBL                                 | 45.600     | 16.384        |

| 2008 | IBM Roadrunner                       | 1.105.000  | $124.400^{1}$ |

| 2009 | Jaguar am ORNL, Cray                 | 1.759.000  | $224.162^2$   |

<sup>&</sup>lt;sup>1</sup>Anzahl der Kerne (6.480 Opteron, 12.960 Cell)

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

# Moore's Law: Formel und Beispiele

$$L(t) = L(0) \times 2^{t/18}$$

mit: L(t) = Leistung zum Zeitpunkt t, L(0) = Leistung zum Zeitpunkt 0, und Zeit t in Monaten.

Einige Formelwerte: Jahr 1: 1,5874

Jahr 2: 2,51984

Jahr 3: 4

Jahr 5: 10,0794

Jahr 6: 16

Jahr 7: 25,3984

Jahr 8: 40,3175

4. iviader

Oniversitat Hambi

64-040 Rechnerstrukturen

# Moore's Law: Aktuelle Trends

- ► Miniaturisierung schreitet weiter fort

- ▶ aber Taktraten erreichen physikalisches Limit

- ▶ steigender Stromverbrauch, zwei Effekte:

- 1. Leckströme

- 2. proportional zu Taktrate

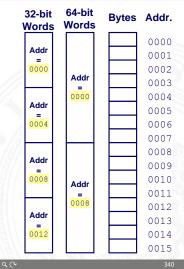

# Entwicklungen

- ▶ 4 GByte Hauptspeicher (und mehr) wird bezahlbar

- ▶ Übergang von 32-bit auf 64-bit Adressierung

- ⇒ Integration mehrerer CPUs auf einem Chip (Dual-/Quad-Core)

- ⇒ zunehmende Integration von Peripheriegeräten

- ⇒ ab 2011: CPU plus leistungsfähiger Grafikchip

- ⇒ **SoC**: "System on a chip"

<sup>&</sup>lt;sup>2</sup>Anzahl der Kerne (Basis: Opteron)

Universität Hamburg

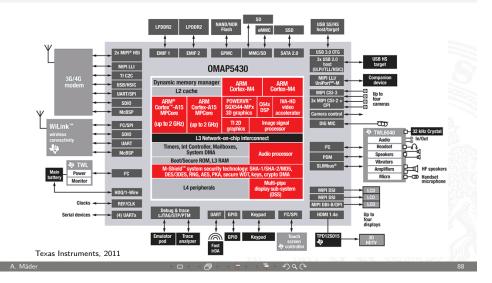

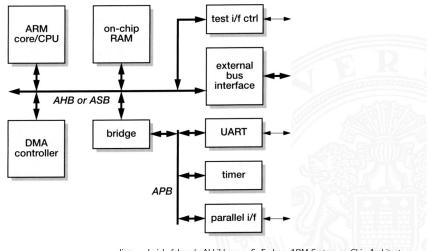

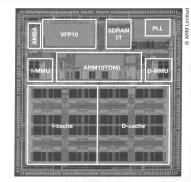

# SoC: System on a chip

#### Gesamtes System auf einem Chip integriert:

- ▶ ein oder mehrere Prozessoren

- ▶ Befehls- und Daten-Caches für die Prozessoren

- ► Hauptspeicher (dieser evtl. auch extern)

- ▶ weitere Speicher für Medien/Netzwerkoperationen

- ▶ Peripherieblöcke nach Kundenwunsch konfiguriert:

- ► serielle und parallele Schnittstellen, I/O-Pins

- Displayansteuerung

- USB, Firewire, SATA

- ► Netzwerk kabelgebunden (Ethernet)

- ► Funkschnittstellen: WLAN, Bluetooth, GSM/UMTS

- ► Feldbusse: I<sup>2</sup>C, CAN, . . .

- ► Handy, Medien-/DVD-Player, WLAN-Router, usw.

Universität Hamburg

# SoC Beispiel: OMAP 5430

- mehrere (verschiedene) CPUs

- ► Grafikbeschleuniger

- ► Chipsatz (Speichercontroller, Interconnect, ...)

- Schnittstellen (WiFi, 4G, USB, Audio, I/O, ...)

#### OMAP5430 Key Benefits

- Designed to drive Smartphones, Tablets and other multimedia-rich mobile devices

- Multi-core ARM® Cortex™ processors

- Two ARM Cortex-A15 MPCore processors capable of speeds up to 2 GHz each

- Two ARM Cortex-M4 processors for low-power offload and real-time responsiveness

- Multi-core POWERVR™ SGX544-MPx graphics accelerators drive 3D gaming and 3D user interfaces

- Dedicated TI 2D BitBlt graphics accelerator

- IVA-HD hardware accelerators enable full HD 1080p60, multi-standard video encode/decode as well as 1080p30 stereoscopic 3D

- Faster, higher-quality image and video capture with up to 24 megapixels (or 12 megapixels S3D) imaging and 1080p60 (or

- Supports four cameras and four displays simultaneously

- Packaging and memory: 14mm x 14mm, 0.4mm pitch PoP dual-channel LPDDR2 memory

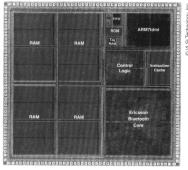

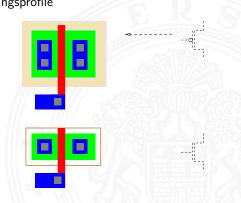

# SoC Beispiel: Bluetooth-Controller - Chiplayout

Figure 13.9 Bluetooth Baseband Controller die photograph

Table 13.1 Bluetooth characteristics

| Process       | 0.25 µm | Transistors | 4,300,000         | MIPS   | 13    |

|---------------|---------|-------------|-------------------|--------|-------|

| Metal layers  | 3       | Die area    | $20 \text{ mm}^2$ | Power  | 75 mW |

| Vdd (typical) | 2.5 V   | Clock       | 0-13 MHz          | MIPS/W | 160   |

# SoC Beispiel: OMAP 5430 (cont.)

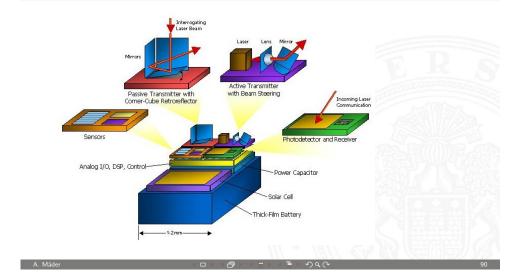

# **Smart Dust**

Wie klein kann man Computer bauen?

► Berkeley Projekt: **Smart Dust**

2002-2006

- ▶ Integration kompletter Rechensysteme auf 1 mm<sup>3</sup>

- CPU, Speicher, I/O vollständiger Digitalrechner

- Sensoren Photodioden, Kompass, Gyro

- Kommunikation Funk, optisch

- ▶ Stromversorgung Photozellen, Batterie, Vibration, Mikroturbine

- ► Echtzeit-Betriebssystem Tiny OS

- ▶ inklusive autonome Vernetzung

- ► Massenfertigung? Tausende autonome Mikrorechner

- "Ausstreuen" in der Umgebung

- vielfältige Anwendungen

Berkeley Sensor & Actuator Center, eecs.berkeley.edu

MIN-Fakultät

Smart Dust: Prototypen

diverse Prototypen:

- vollwertige CPU / Sensoren / RF

- "out-door"-tauglich

- MEMS-"CCR" für opt. Kommunikation

MIN-Fakultät

# Smart Dust: Konzept

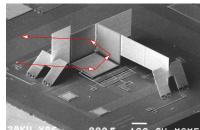

# Smart Dust: Corner-cube reflector ("Katzenauge")

- ► CCR: seitlich zwei starre Spiegel, Gold auf Silizium

- ▶ untere Spiegelfläche beweglich (elektrostatisch, ca. 30 V)

- ▶ gezielte Modulation von eingestrahltem Laserlicht

- ► Reichweiten > 100 m demonstriert

robotics.eecs.berkeley.edu/~pister/SmartDust

64-040 Rechnerstrukturen

# Smart Dust: Energieverbrauch

Miniatur-Solarzellen Wirkungsgrad ca. 3% 26 μW/mm in vollem Sonnenlicht

Batterien:  $\sim 1 \text{J/mm}^{\frac{1}{2}}$  Kondensatoren:  $\sim 10 \text{ mJ/mm}^{\frac{1}{2}}$

Solarzellen:  $\sim 0.1 \text{ mW/mm}$   $\sim 1 \text{J/mm/day}$  (außen,Sonne)

$\sim 10~\mu W/mm~\sim 10 mJ/mm~/day~~(innen)$

$Digital schaltung \hspace{1cm} 1 \hspace{1mm} n J/instruction \hspace{1cm} (Strong Arm \hspace{1mm} SA1100)$

Analoger Sensor 1 nJ/sample

Kommunikation 1 nJ/bit (passive transmitter, s.u.)

opt. digitale ASICs:  $\sim 5 \text{ pJ/bit}$  (LFSR Demonstrator, 1.4V)

A. Madei

MIN-Fakultät

3.3 Moore's Law - Roadman und Grenzen des Wachstur

64-040 Rechnerstrukturen

# Roadmap: ITRS

International Technology Roadmap for Semiconductors

http://www.itrs.net/reports.html

- ▶ non-profit Organisation

- diverse Fördermitglieder

- ► Halbleiterhersteller

- Geräte-Hersteller

- ► Unis, Forschungsinstitute

- ► Fachverbände aus USA, Europa, Asien

- ▶ Jährliche Publikation einer langjährigen Vorhersage

- ► Zukünftige Entwicklung der Halbleitertechnologie

- ► Komplexität typischer Chips (Speicher, Prozessoren, SoC, ...)

- Modellierung, Simulation, Entwurfssoftware

MIN-Fakultät Fachbereich Informatik

.3 Moore's Law - Roadmap und Grenzen des Wachstums

-040 Rechnerstrukturen

#### Grenzen des Wachstums

- ▶ Jeder exponentielle Verlauf stößt irgendwann an natürliche oder wirtschaftliche Grenzen.

- ▶ Beispiel: eine DRAM-Speicherzelle speichert derzeit etwa 100.000 Elektronen. Durch die Verkleinerung werden es mit jeder neuen Technologiestufe weniger.

- ▶ Offensichtlich ist die Grenze spätestens erreicht, wenn nur noch ein einziges Elektron gespeichert würde.

- ► Ab diesem Zeitpunkt gibt es bessere Performance nur noch durch bessere Algorithmen / Architekturen

- ▶ Annahme: 50 % Wachstum pro Jahr,  $a^b = \exp(b \cdot \ln a)$

- ▶ Elektronen pro Speicherzelle:  $100000/(1.5^{x/Jahre}) \ge 1$ .

- $x = \ln(100.000) / \ln(1.5) \approx 28$  Jahre

\_ ,,,

9

MIN-Fakultät Fachbereich Informatik

B Moore's Law - Roadmap und Grenzen des Wachstum

64-040 Rechnerstrukturer

# Moore's Law: Schöpferische Pause

Beispiel für die Auswirkung von Moore's Law.

Angenommen die Lösung einer Rechenaufgabe dauert derzeit vier Jahre, und die Rechenleistung wächst jedes Jahr um 60 %.

Wie lösen wir das Problem?

# Moore's Law: Schöpferische Pause

Beispiel für die Auswirkung von Moore's Law.

Angenommen die Lösung einer Rechenaufgabe dauert derzeit vier Jahre, und die Rechenleistung wächst jedes Jahr um 60 %.

Ein mögliches Vorgehen ist dann das folgende:

- ▶ Wir warten drei Jahre, kaufen dann einen neuen Rechner und erledigen die Rechenaufgabe in einem Jahr.

- ▶ Wie das ?

MIN-Fakultät

# Wie geht es jetzt weiter?

Ab jetzt erst mal ein bottom-up Vorgehen: Start mit grundlegenden Aspekten, dann Kennenlernen aller Komponenten des Digitalrechners und Konstruktion eines vollwertigen Rechners.

- ► Grundlagen der Repräsentation von Information

- ► Darstellung von Zahlen und Zeichen

- ▶ arithmetische und logische Operationen

- ► Vorkenntnisse nicht nötig (aber hilfreich)

MIN-Fakultät

# Moore's Law: Schöpferische Pause

Beispiel für die Auswirkung von Moore's Law.

Angenommen die Lösung einer Rechenaufgabe dauert derzeit vier Jahre, und die Rechenleistung wächst jedes Jahr um 60 %.

Ein mögliches Vorgehen ist dann das folgende:

- ▶ Wir warten drei Jahre, kaufen dann einen neuen Rechner und erledigen die Rechenaufgabe in einem Jahr.

- ⇒ Nach einem Jahr können wir einen Rechner kaufen, der um den Faktor 1.6 Mal schneller ist, nach zwei Jahren bereits  $1.6 \times 1.6$ Mal schneller, und nach drei Jahren (also am Beginn des vierten Jahres) gilt  $(1 + 60 \%)^3 = 4,096$ .

- ▶ Wir sind also sogar ein bisschen schneller fertig, als wenn wir den jetzigen Rechner die ganze Zeit durchlaufen lassen.

# Gliederung

- 4. Information

Definition und Begriff Informationsübertragung Zeichen

Gliederung (cont.)

# MIN-Fakultät

MIN-Fakultät

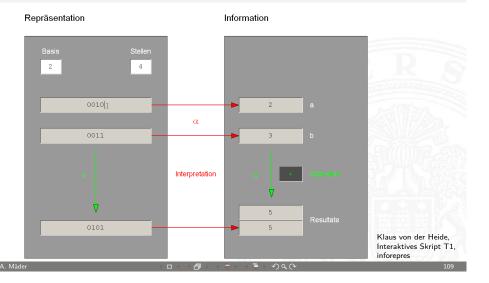

Information

- ▶ **Information** ~ abstrakter Gehalt einer Aussage

- ▶ Die Aussage selbst, mit der die Information dargestellt bzw. übertragen wird, ist eine Repräsentation der Information

- ▶ Das Ermitteln der Information aus einer Repräsentation heißt Interpretation

- ▶ Das Verbinden einer Information mit ihrer Bedeutung in der realen Welt heißt Verstehen

MIN-Fakultät

# Repräsentation (Beispiele)

Beispiel: Mit der Information "25" sei die abstrakte Zahl gemeint, die sich aber nur durch eine Repräsentation angeben lässt:

► Text deutsch: fünfundzwanzig

► Text englisch: twentyfive

Zahl römisch: XXV

► Zahl dezimal: 25

Zahl binär: 11001

► Zahl Dreiersystem: 221

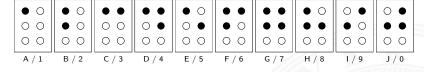

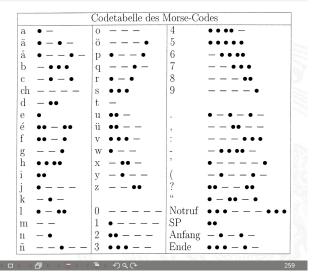

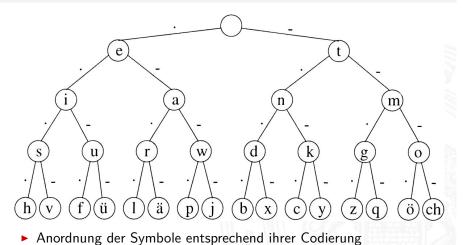

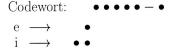

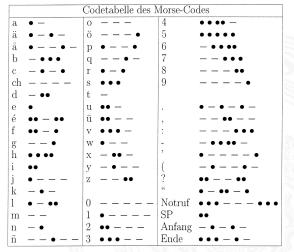

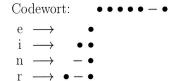

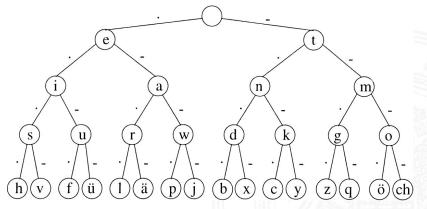

Morse-Code:

▶ Wo auch immer Repräsentationen auftreten, meinen wir eigentlich die Information, z.B.:

$$5\cdot(2+3)=25$$

- ▶ Die Information selbst kann man überhaupt nicht notieren (!)

- ► Es muss immer Absprachen geben über die verwendete Repräsentation. Im obigen Beispiel ist implizit die Dezimaldarstellung gemeint, man muss also die Dezimalziffern und das Stellenwertsystem kennen.

- ▶ Repräsentation ist häufig mehrstufig, z.B.

Zahl: Dezimalzahl 347

Ziffer: 4-bit binär 0011 0100 0111 elektrische Spannung 0.1V 0.1V 3.3V 3.3V ... Bit:

# Repräsentation vs. Ebenen

In jeder (Abstraktions-) Ebene gibt es beliebig viele Alternativen der Repräsentation

- ► Auswahl der jeweils effizientesten Repräsentation

- unterschiedliche Repräsentationen je nach Ebene

- ightharpoonup Beispiel: Repräsentation der Zahl  $\pi=3.1415\ldots$  im

- 80-bit Binärdaten, Spannungen ▶ x86 Prozessor Hauptspeicher 64-bit Binärdaten, Spannungen codierte Zahl, magnetische Bereiche Festplatte CD-ROM codierte Zahl, Land/Pits-Bereiche Papier Text, "3.14159265..."

# Information vs. Repräsentation

- ▶ Information: Wissen um oder Kenntnis über Sachverhalte und Vorgänge (Der Begriff wird nicht informationstheoretisch abgestützt, sondern an umgangssprachlicher Bedeutung orientiert).

- ▶ Nachricht: Zeichen oder Funktionen, die Informationen zum Zweck der Weitergabe aufgrund bekannter oder unterstellter Abmachungen darstellen (DIN 44300).

- ▶ Beispiel für eine Nachricht: Temperaturangabe in Grad Celsius oder Fahrenheit.

- ▶ Die Nachricht ist also eine Darstellung von Informationen und nicht der Übermittlungsvorgang

# Information vs. Nachricht

- Aussagen

- N1 Er besucht General Motors

- N2 Unwetter am Alpenostrand

- N3 Sie nimmt ihren Hut

- ► Alle Aussagen sind aber doppel/mehrdeutig:

- N1 Firma? Militär?

- N2 Alpen-Ostrand? Alpeno-Strand?

- N3 tatsächlich oder im übertragenen Sinn?

- ⇒ Interpretation: Es handelt sich um drei Nachrichten, die jeweils zwei verschiedene Informationen enthalten

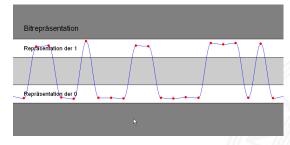

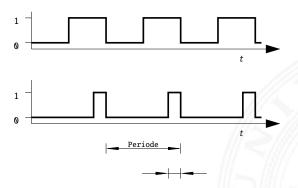

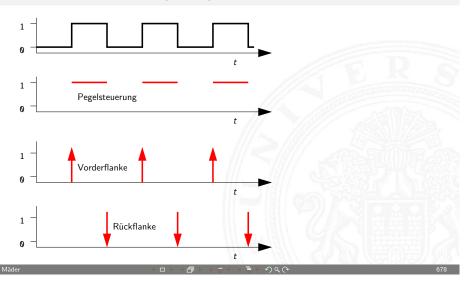

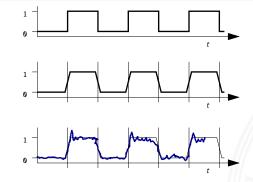

# Beispiel: Binärwerte in 5 V-CMOS-Technologie

Klaus von der Heide, Interaktives Skript T1, demobitrep

- ► Spannungsverlauf des Signals ist kontinuierlich

- ► Abtastung zu bestimmten Zeitpunkten

- ▶ Quantisierung über abgegrenzte Wertebereiche:

- ▶  $0.0 V \le a(t) \le 1.2 V$ : Interpretation als 0

- ▶  $3.3 V \le a(t) \le 5.0 V$ : Interpretation als 1

- außerhalb und innerhalb: ungültige Werte

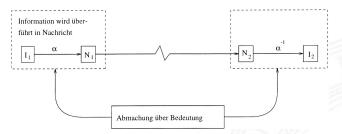

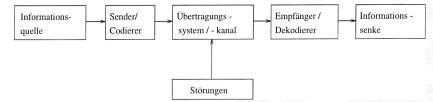

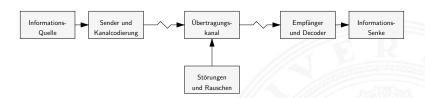

# Modell der Informationsübertragung

#### Beschreibung der Informationsübermittlung:

- ▶ die Nachricht  $N_1$  entsteht durch Abbildung  $\alpha$  aus der Information  $I_1$

- ▶ Übertragung der Nachricht an den Zielort

- ▶ Umkehrabbildung  $\alpha^{-1}$  aus der Nachricht  $N_2$  liefert die Information  $I_2$

4.2 Information - Informationsübertragung

64-040 Rechnerstrukturen

# Demo: Information vs. Repräsentation

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

# Nachrichtentechnisches Modell der Informationsübertragung

#### Beispiele für Störungen:

- ► Bitfehler beim Speichern

- ► Störungen beim Funkverkehr

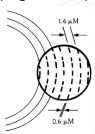

- ► Schmutz oder Kratzer auf einer CD/DVD

- usw.

ler Russian Park

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

Informationstreue

Ergibt  $\alpha$  gefolgt von  $\sigma$  dasselbe wie  $\nu$  gefolgt von  $\alpha'$ , dann heißt  $\nu$  **informationstreu**.

- lacktriangleright mit lpha' als der Interpretation des Resultats der Operation u

- lacktriangle häufig sind lpha und lpha' gleich, aber nicht immer

- $ightharpoonup \sigma$  injektiv: **Umschlüsselung**

- $\triangleright \nu$  injektiv: **Umcodierung**

- ▶  $\sigma$  innere Verknüpfung der Menge  $\mathcal{J}$  und  $\nu$  innere Verknüpfung der Menge  $\mathcal{R}$ : dann ist  $\alpha$  ein Homomorphismus der algebraischen Strukturen  $(\mathcal{J}, \sigma)$  und  $(\mathcal{R}, \nu)$ .

- $ightharpoonup \sigma$  bijektiv: Isomorphismus

# Informationstreue (cont.)

Welche mathematischen Eigenschaften gelten bei der Informationsverarbeitung, in der gewählten Repräsentation?

#### Beispiele:

- ▶ Gilt  $x^2 > 0$ ?

- ► float:

- signed integer: nein

- ► Gilt (x + y) + z = x + (y + z)?

- integer:

nein

- ▶ float:

- 1.0E20 + (-1.0E20 + 3.14) = 0

- ▶ Details: später

# Binärzeichen

- ▶ Binärzeichen (engl. binary element, binary digit, bit): Jedes der Zeichen aus einem Vorrat / aus einer Menge von zwei Symbolen.

- ► Beispiel:

- $\mathcal{Z}_1 = \{0,1\}$

- $\triangleright \mathcal{Z}_2 = \{\text{high, low}\}\$

- $\triangleright \mathcal{Z}_3 = \{\text{rot, grün}\}\$

- $\mathcal{Z}_4 = \{+, -\}$

# Beschreibung von Information durch Zeichen

- ▶ Zeichen (engl. character): Element z aus einer zur Darstellung von Information vereinbarten, einer Abmachung unterliegenden, endlichen Menge Z von Elementen.

- ▶ Die Menge heißt **Zeichensatz** oder **Zeichenvorrat** (engl. character set).

- ► Beispiel:

- $\mathcal{Z}_1 = \{0, 1\}$

- $\triangleright \mathcal{Z}_2 = \{0, 1, 2, \dots, 9, A, B, C, D, E, F\}$

- $\triangleright \mathcal{Z}_3 = \{\alpha, \beta, \gamma, \dots, \omega\}$

- $\triangleright \mathcal{Z}_4 = \{CR, LF\}$

MIN-Fakultät

# **Alphabet**

- ▶ **Alphabet** (engl. *alphabet*): Ein in vereinbarter Reihenfolge geordneter Zeichenvorrat  $\mathcal{A} = \mathcal{Z}$

- Beispiel:

- $\rightarrow A_1 = \{0,1,2,\ldots, 9\}$

- $ightharpoonup \mathcal{A}_2 = \{So,Mo,Di,Mi,Do,Fr,Sa\}$

- $\rightarrow A_3 = \{ 'A', 'B', ..., 'Z' \}$

- ▶ Numerischer Zeichensatz: Zeichenvorrat aus Ziffern und/oder Sonderzeichen zur Darstellung von Zahlen

- ► Alphanumerischer Zeichensatz: Zeichensatz aus (mindestens) den Dezimalziffern und den Buchstaben des gewöhnlichen Alphabets, meistens auch mit Sonderzeichen (Leerzeichen, Punkt, Komma usw.)

64-040 Rechnerstrukturen

# Zeichenkette

- ▶ **Zeichenkette** (engl. *string*): Eine Folge von Zeichen

- ▶ Wort (engl. word): Eine Folge von Zeichen, die in einem gegebenen Zusammenhang als Einheit bezeichnet wird. Worte mit 8 Bit werden als Byte bezeichnet.

- ▶ **Stelle** (engl. *position*): Die Lage/Position eines Zeichens innerhalb einer Zeichenkette.

- Beispiel

- $\triangleright$  s = H e l l o , w o r l d !

MIN-Fakultät Fachbereich Informatik

5 Zahldarstellung

# Gliederung (cont.)

#### Literatur

- 6 Arithmetik

- 7. Textcodierung

- 8. Boole'sche Algebra

- 9. Logische Operationen

- 10. Codierung

- 11. Schaltfunktionen

- 12. Schaltnetze

- 13. Zeitverhalten

- 14 Schaltwerke

- 15. Grundkomponenten für Rechensysteme

- VLSI-Entwurf und -Technologie

- Rechnerarchitektur

MIN-Fakultät Fachbereich Informatik

5 Zahldarstellung

-040 Rechnerstrukturen

# Gliederung

- 1. Einführung

- 2. Digitalrechner

- 3. Moore's Law

- 4. Informatio

- 5. Zahldarstellung

Konzept der Zahl

Stellenwertsystem

Umrechnung zwischen verschiedenen Basen

Zahlenbereich und Präfixe

Festkommazahlen

Darstellung negativer Zahlen

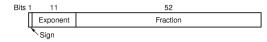

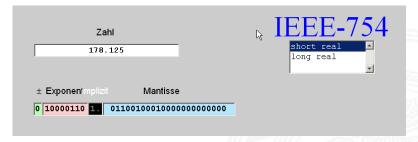

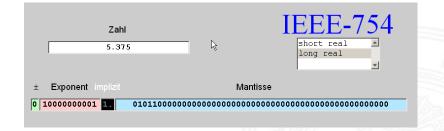

Gleitkomma und IEEE 754

Maschinenworte

MIN-Fakultät Fachbereich Informatik

54.040 D. I. . . I.

# Gliederung (cont.)

- 18. Instruction Set Architecture

- 19. Assembler-Programmierung

- 20. Computerarchitektur

- 21. Speicherhierarchie

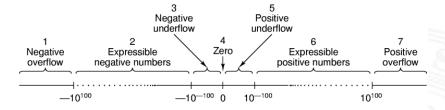

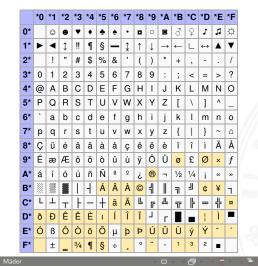

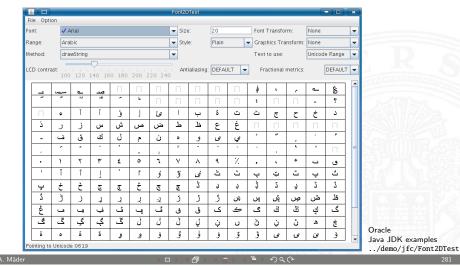

# Darstellung von Zahlen und Zeichen: Übersicht

- ► Natürliche Zahlen (engl. integer numbers)

- ► Festkommazahlen (engl. fixed point numbers)

- ► Gleitkommazahlen (engl. *floating point numbers*)

- ► Aspekte der Textcodierung

- ► Ad-hoc Codierungen

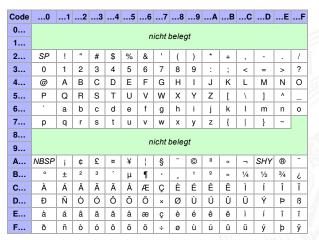

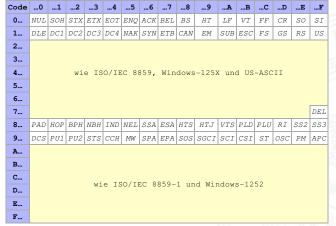

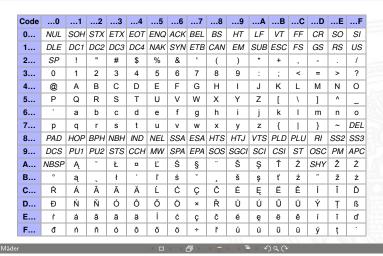

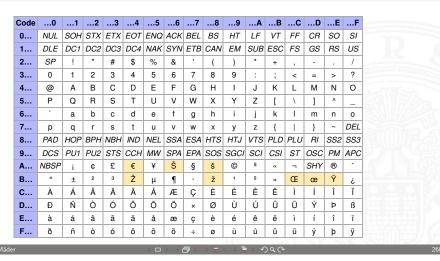

- ► ASCII und ISO-8859-1

- ► Unicode

- ► Pointer (Referenzen, Maschinenadressen)

# Eigenschaften eines Zahlensystems

- ► Zahlenbereich: kleinste und größte darstellbare Zahl?

- ► Darstellung negativer Werte?

- ► Darstellung gebrochener Werte?

- ► Darstellung sehr großer Werte?

- ▶ Unterstützung von Rechenoperationen? Addition, Subtraktion, Multiplikation, Division, etc.

- ► Abgeschlossenheit unter diesen Operationen?

- ▶ Methode zur dauerhaften Speicherung/Archivierung?

- ► Sicherheit gegen Manipulation gespeicherter Werte?

MIN-Fakultät

# Konzept der Zahl

- ▶ das Messen ist der Ursprung der Zahl

- ▶ als Abstraktion der Anzahl von Objekten

- die man abzählen kann

- ► Anwendung des Distributivgesetzes:

- 2 Äpfel + 5 Äpfel = 7 Äpfel

- 2 Birnen + 5 Birnen = 7 Birnen

$\Rightarrow$  2 + 5 = 7

MIN-Fakultät

# Literaturtipp

Georges Ifrah Universalgeschichte der Zahlen

Universität Hamburg

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

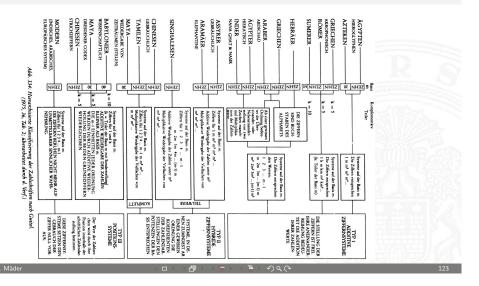

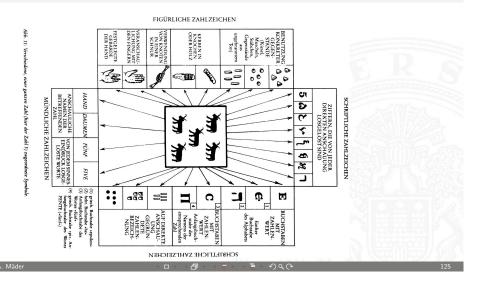

# Klassifikation verschiedener Zahlensysteme

#

Direkte Wahrnehmung vs. Zählen

Abb. 1: Auf einen Blick können wir mit unserer direkten Zahlenwahrnehmung feststellen, ob eine Gesamtbeit ein, zwei, drei oder vier Elemente umfaßt; Mengen, die größer sind, mässen wir messtens »zählen» – oder mit Hilfe des Vergleichs oder der gedanklichen Aufteilung in Teilmengen erfassen –, da unsere direkte Wahrnehmung nicht mehr ausreicht, exakte Angaben zu machen.

90

UH

Universität Hamburg

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

#### i.1 Zanidarstellung - Konzept der Zani

# Abstraktion: Verschiedene Symbole für eine Zahl

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

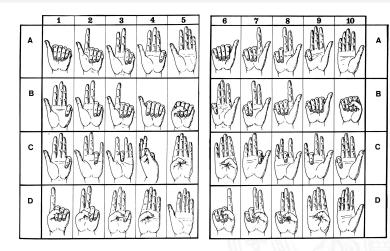

# Zählen mit den Fingern ("digits")

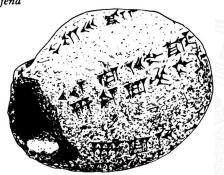

# Speicherung: Tonbörse: 15. Jh. v. Chr.

Gegenstände, Hammel und Ziegen betreffend

- 21 Mutterschafe

- 6 weibliche Lämmer

- 8 erwachsene Hammel

- 4 männliche Lämmer

- 6 Mutterziegen

- 1 Bock

- (2) Jungziegen

Abb. 3: Eiförmige Tonbörse (46 mm × 62 mm × 50 mm), entdeckt in den Ruinen des Palastes von Nuzi (mesopotamische Stadt; ca. 15. Jh. v. Chr.). (Harvard Semitic Museum, Cambridge. Katalognummer SMN 1854)

48 Tonkügelchen im Inneren: tamper-proof

MIN-Fakultät

Jniversität Hamburg

# Speicherung: Knotenschnüre

Abb. 66: Interpretation eines quipu: Die Zahl 658 auf der Schnur E ist gleich der Summe der Zahlen auf den Schnüren A, B, C und D. Dieses Bündel ist das erste an einem peruanischen quipu. (American Museum of Natural History, New York, B 8713: vol. Leland Locke 1923)

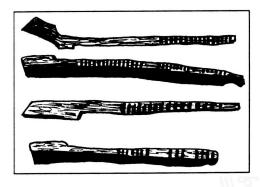

# Speicherung: Kerbhölzer

Abb. 58: Kerbhölzer aus Bäckereien in Frankreich, wie sie in kleinen Ortschaften auf dem Lande üblich waren.

Abb. 59: Englische Kerbhölzer aus dem 13. lahrhundert. (Sammlung Society of Antiquaries, London; Zeichnung nach Menninger 1957/58, II, 42)

Universität Hamburg

# Rechnen: Römische Ziffern

- ► Ziffern: I=1, V=5, X=10, L=50, C=100, D=500, M=1000

- ▶ Werte eins bis zehn: I, II, III, IV, V, VI, VII, VIII, IX, X

- ▶ Position der Ziffern ist signifikant:

- ▶ nach Größe der Ziffernsymbole sortiert, größere stehen links

- ▶ andernfalls Abziehen der kleineren von der größeren Ziffer

- ► IV=4, VI=6, XL=40, LXX=70, CM=900

- ▶ heute noch in Gebrauch: Jahreszahlen, Seitennummern, usw. Beispiele: MDCCCXIII=1813, MMIX=2009

- keine Symbole zur Darstellung großer Zahlen

- Rechenoperationen so gut wie unmöglich

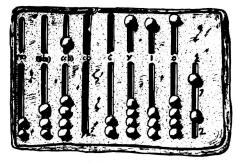

# Römischer Abakus

Abb. 87: Römischer Handabakus. (Cabinet des Médailles, Bibliothèque Natio-

5.2 Zahldarstellung - Stellenwertsystem

64-040 Rechnerstrukture

# Das Stellenwertsystem ("Radixdarstellung")

- ► Wahl einer geeigneten Zahlenbasis b ("Radix")

- ▶ 10: Dezimalsystem

- ▶ 16: Hexadezimalsystem (Sedezimalsystem)

- 2: Dualsystem

- ▶ Menge der entsprechenden Ziffern  $\{0, 1, ..., b-1\}$

- ▶ inklusive einer besonderen Ziffer für den Wert Null

- ▶ Auswahl der benötigten Anzahl *n* von Stellen

$$|z| = \sum_{i=0}^{n-1} a_i \cdot b^i$$

b Basis a<sub>i</sub> Koeffizient an Stelle i

universell verwendbar, für beliebig große Zahlen

# Römischer Abakus

Dagegen können im Rahmen einer entwickelten Stellenwertschrift nicht nur alle beliebigen Zahlen jeder Größenordnung mit einer beschränkten Anzahl von Ziffern dargestellt werden, sondern mit ihr kann auch sehr einfach gerechnet werden. Und eben deshalb ist unser Ziffernsystem eine der Grundlagen der geistigen Fähigkeiten der modernen Menschen.

Als Beweis dafür führen wir mit römischen Ziffern eine einfache Addition durch:

| CCLXVI     | 266   |

|------------|-------|

| MDCCCVII   | 1 807 |

| DCL        | 650   |

| MLXXX      | 1 080 |

| MMMDCCCIII | 3 803 |

Ohne Übertragung auf unsere Zahlschrift wäre das sehr schwierig, wenn nicht unmöglich – und dabei handelt es sich doch bloß um eine Addition! Wie verhielte sich das erst bei einer Multiplikation oder gar bei einer Division? Mit diesen Ziffernsystemen kann nicht gerechnet werden, da ihre Grundziffern einen festgelegten Zahlenwert haben. Diese Ziffern sind keine Recheneinheiten, sondern Abkürzungen, mit denne Ergebnisse von Rechnungen festgehalten werden können, die mit Gegenständen auf der Rechentafel, dem Abakus oder dem Kugelbrett bereits gelöst worden waren.

5.2 Zahldarstellung - Stellenwertsyster

64-040 Rechnerstrukturen

# Einführung der Null: Babylon, 3 Jh. v. Chr.

Abb. 289- Mathematische Tafel aus Uruk; sie wurde bei Schwarzgrabungen gefunden and stammt aus dem 2. oder 3. fb. v. Chr. Et handelt sich um eines der ältesten bekannten Zeugnisse für die Verwendung der babylonischen Null. (Musie du Louvre, Taf. AO 6484, Rück-

(Musée du Louvre, Taf. AO 6484, Rückseite; Thureau-Dangin 1922, Nr. 33, Taf. 62; 1938, 76-81. Unveröffentl. Kopie d. Verf.)

:88:

Rechnerstrukturen

# Babylon: Beispiel mit Satz des Pythagoras

|     | 1 rans                     | kription          |                    |        | _   |

|-----|----------------------------|-------------------|--------------------|--------|-----|

| 1 2 | SAMELIL-TI SI-LI-IP-TIM    | ÍB-SÁ SAG<br>G-IÚ | ÍB-SÁ SI-LI-IP-TIM | MU-BI- | 114 |

| 3   | 1 10 115                   | 1; 59             | 2,49               | ΚI     |     |

| 4   | 14 50,6, 58, 14, 50,6,15   | 56.7              | 3.12:1             | KI     |     |

| 5   | 1 58, 41, 15, 33, 45       | 1, 16 , 41        | 1.50.49            | KI     |     |

| 6   | 1 59 10 2 29 32 52 16      | 3,31,49           | 5.9.1              | KL.    | _   |

| 7   | 1,48,54, 1,40              | 1,5               | 1 . 37             | KI     | 15  |

| В   | 1 47 6 41,40               | 5 : 19            | 8.1                | KI     | , ( |

| 9   | 1 43, 11,56 , 28 , 26 , 40 | 38 , 11           | 59 ; 1             | KI     | 7   |

| 0   | 1 2 45                     | 13 . 19           | 20 : 49            | KI     | 8   |

| 1   | 1 38, 33,36,36             | 9.1               | 12 . 49            | KI     | 9   |

| 2   |                            | 1, 22 . 41        | 2 . 16 . 1         | KI     | 10  |

| 3   | 1 33, 45                   | 45                | 1 . 15             | KI     | 11  |

| 4   |                            | 27.59             | 48 . 49            | KI     | 12  |

|     |                            | 7 , 12 , 1        | 4.49               | KI     | 13  |

| 6   | 1 25 48, 51,35 6,40        | 29,31             | 53 , 49            | KI     | A.  |

| 7   | 11 23 : 13 46 . 40         | 40                | 50   11            | V1 .   | 240 |

\*Leerstelle, die das Fehlen von Einheiten einer bestimmten Größenordnung bezeichnet.

Abb. 288: Rechentafel aus der Zeit um 1800–1700 v. Chr.; ihr Inhalt belegt, daß die babylonischen Mathematiker zur Zeit der I. Dynastie bereits den «Satz des Pythagoras» kannten

(Columbia University of New York, Tafel Plimpton 322; unveröffentl. Kopie d. Verf.; vgl. Neugebauer/Sachs 1945, 38-41, Taf. 25)

A. Mäder

· 酉 × × = × × = × 夕久(?

MIN-Fakultät ich Informatik

5 2 7ahldarstellung - Stellenwertsystem

Universität Hamburg

64-040 Rechnerstrukturen

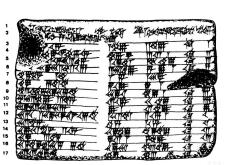

# Babylon: Beispiel Potenztabelle 100<sup>i</sup>

Klaus von der Heide Interaktives Skript T1 powersbabylon 5.2 Zahldarstellung - Stellenwertsysten

4-040 Rechnerstrukturen

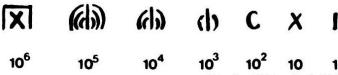

# Babylon: Sexagesimalsystem

- ► Einführung vor ungefähr 4000 Jahren, erstes Stellenwertsystem

- ▶ Basis 60

- ▶ zwei Symbole: | = 1 und < = 10

- ► Einritzen gerader und gewinkelter Striche auf Tontafeln

- ▶ Null bekannt, aber nicht mitgeschrieben

- ► Leerzeichen zwischen zwei Stellen

- ► Beispiele für Zahlen:

► ||||| 5 ► <<||| 2

| < <  $90 = 1 \cdot 60 + 3 \cdot 10$

**|** <<|

$3621 = 1 \cdot 3600 + 0 \cdot 60 + 2 \cdot 10 + 1$

▶ für Zeitangaben und Winkeleinteilung heute noch in Gebrauch

MIN-Fakultät Fachbereich Informatik

64.040.D. I. . I.

# Dezimalsystem

Number =

$$\sum_{i=-k}^{n} d_i \times 10^i$$

- ▶ das im Alltag gebräuchliche Zahlensystem

- ► Einer, Zehner, Hunderter, Tausender, usw.

- ► Zehntel, Hundertstel, Tausendstel, usw.

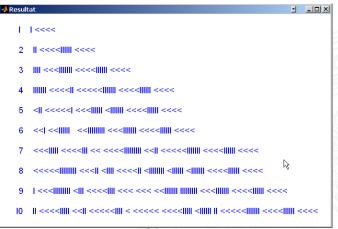

# Dualsystem

- ► Stellenwertsystem zur Basis 2

- ▶ braucht für gegebene Zahl ca. dreimal mehr Stellen als Basis 10

- ▶ für Menschen daher unbequem besser Oktal- oder Hexadezimalschreibweise, s.u.

- ▶ technisch besonders leicht zu implementieren

- weil nur zwei Zustände unterschieden werden müssen

- ▶ z.B. zwei Spannungen, Ströme, Beleuchtungsstärken s.o.: Kapitel 4: Information - Binärwerte. . .

- robust gegen Rauschen und Störungen

- einfache und effiziente Realisierung von Arithmetik

# Addition im Dualsystem

- ▶ funktioniert genau wie im Dezimalsystem

- ► Addition mehrstelliger Zahlen erfolgt stellenweise

- Additionsmatrix:

$$\begin{array}{c|cccc} + & 0 & 1 \\ \hline 0 & 0 & 1 \\ 1 & 1 & 10 \\ \end{array}$$

Beispiel

| Stelle         | Wert im Dualsystem | Wert im Dezimalsystem |     |

|----------------|--------------------|-----------------------|-----|

| $2^{0}$        | 1                  | 1                     |     |

| $2^1$          | 10                 | 2                     |     |

| $2^{2}$        | 100                | 4                     |     |

| $2^3$          | 1000               | 8                     |     |

| $2^{4}$        | 1 0000             | 16                    |     |

| $2^{5}$        | 10 0000            | 32                    |     |

| $2^{6}$        | 100 0000           | 64                    |     |

| 27             | 1000 0000          | 128                   |     |

| 2 <sup>8</sup> | 1 0000 0000        | 256                   |     |

| $2^{9}$        | 10 0000 0000       | 512                   |     |

| $2^{10}$       | 100 0000 0000      | 1024                  |     |

|                |                    |                       |     |

| √läder         | <□> < <b>□</b> >   | < = > < € > 10 Q (°   | 140 |

# Multiplikation im Dualsystem

- ▶ funktioniert genau wie im Dezimalsystem

- $ightharpoonup p = a \cdot b$  mit Multiplikator a und Multiplikand b

- ▶ Multiplikation von a mit je einer Stelle des Multiplikanten b

- Addition der Teilterme

- ► Multiplikationsmatrix ist sehr einfach:

$$\begin{array}{c|cccc} \times & 0 & 1 \\ \hline 0 & 0 & 0 \\ 1 & 0 & 1 \\ \end{array}$$

= 2327

$= 0 \times 917$

$= 1001\,0001\,0111$

64-040 Rechnerstrukturen

# Multiplikation im Dualsystem (cont.)

Beispiel

| 10110011 $\times$ | 1101 | $= 179 \cdot 13$ |

|-------------------|------|------------------|

| 10110011          | 1    | _                |

| 10110011          | 1    |                  |

| 00000000          | 0    |                  |

| 10110011          | 1    |                  |

| Ü 11101111        |      | ///>             |

| 100100010111      |      | ///<             |

|                   |      |                  |

. Mäder ⟨□⟩⟨∰⟩⟨Ξ⟩⟨≒⟩⟨⟨€

MIN-Fakultät Fachbereich Informatik

5.2 Zahldarstellung - Stellenwertsystem

64-040 Rechnerstrukture

### Hexadezimalsystem

- ▶ Basis 16

- ► Zeichensatz ist {0, 1, 2, ..., 9, A, B, C, D, E, F}

- ► C-Schreibweise mit Präfix 0x Klein- oder Großbuchstaben

- ▶ viel leichter lesbar als entsprechende Dualzahl

- ► Umwandlung aus/vom Dualsystem: Zusammenfassen bzw. Ausschreiben von je vier Bits:

$$\begin{split} 0x0 &= 0000, 0x1 = 0001, 0x2 = 0010, \dots, 0x9 = 1001, \\ 0xA &= 1010, 0xB = 1011, 0xC = 1100, 0xD = 1101, 0xE = 1110, 0xF = 1111 \end{split}$$

MIN-Fakultät Fachbereich Informatik

5.2 Zahldarstellung - Stellenwertsystem

4-040 Rechnerstrukturen

# Oktalsystem

- ► Basis 8

- ► Zeichensatz ist {0, 1, 2, 3, 4, 5, 6, 7}

- ► C-Schreibweise mit führender Null als Präfix:

$$\begin{array}{lll} \bullet & 0001 = & 1_{10} \\ 0013 = & 11_{10} = & 1 \cdot 8 + 3 \\ 0375 = 253_{10} = 3 \cdot 64 + 7 \cdot 8 + 5 \\ \text{usw.} \end{array}$$

- ⇒ Hinweis: also führende Null in C für Dezimalzahlen unmöglich

- ▶ für Menschen leichter lesbar als Dualzahlen

- Umwandlung aus/vom Dualsystem durch Zusammenfassen bzw. Ausschreiben von je drei Bits:

$$00 = 000, 01 = 001, 02 = 010, 03 = 011,$$

$04 = 100, 05 = 101, 06 = 110, 07 = 111$

A. Mäder

> < 🗗 > < = > < = > 90

MIN-Fakultät

Universität Hamburg

64-040 Rechnerstrukturen

# Beispiel: Darstellungen der Zahl 2001

```

Binary 1 1 1 1 1 1 0 1 0 0 0 1 1 1 \times 2^{10} + 1 \times 2^9 + 1 \times 2^8 + 1 \times 2^7 + 1 \times 2^6 + 0 \times 2^5 + 1 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 0 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 0 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 0 \times 2^4 + 0 \times 2^3 + 0 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 0 \times 2^3 + 0 \times 2^3

```

# Umrechnung Dual-/Oktal-/Hexadezimalsystem

#### Example 1

Hexadecimal 1 9 4 8 B 6

Binary 0001100101000.101101100

Octal 1 4 5 1 0 . 5 5 4

#### Example 2

Hexadecimal 7 B A 3 B C 4

Binary 01111101110100011.1011111000100

Octal 7 5 6 4 3 5 7 0 4

- ► Gruppieren von jeweils 3 bzw. 4 Bits

- ▶ bei Festkomma vom Dezimalpunkt aus nach außen

. Mäder

3 7ahldarstellung - Umrechnung zwischen verschiedenen Baser

64-040 Rechnerstrukturen

# Umwandlung über Potenztabellen

Vorgehensweise für Integerzahlen:

- ➤ Subtraktion des größten Vielfachen einer Potenz des Zielsystems (gemäß der vorberechneten Potenztabelle) von der umzuwandelnden Zahl

- ► Notation dieses größten Vielfachen (im Zielsystem)

- ► Subtraktion wiederum des größten Vielfachen vom verbliebenen Rest

- ► Addition des zweiten Vielfachen zum ersten

- ightharpoonup Wiederholen, bis Rest = 0

MIN-Fakultät Fachbereich Informatik

5.3 Zahldarstellung - Umrechnung zwischen verschiedenen Basen

4-040 Rechnerstrukturen

Basis: 60

# Umrechnung zwischen verschiedenen Basen

- ► Menschen rechnen im Dezimalsystem

- ► Winkel- und Zeitangaben auch im Sexagesimalsystem

- ▶ Digitalrechner nutzen (meistens) Dualsystem

- ► Algorithmen zur Umrechnung notwendig

- ► Exemplarisch Vorstellung von drei Varianten:

- 1. vorberechnete Potenztabellen

- 2. Divisionsrestverfahren

- 3. Horner-Schema

r

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukture

# Potenztabellen Dual/Dezimal

| Stelle         | Wert | Ste             | lle Wert im Dualsystem                  |

|----------------|------|-----------------|-----------------------------------------|

| $2^{0}$        | 1    | 10 <sup>0</sup> | 1                                       |

| $2^1$          | 2    | $10^{1}$        | 1010                                    |

| $2^{2}$        | 4    | $10^{2}$        | 110 0100                                |

| $2^{3}$        | 8    | $10^{3}$        | 111 1101 0000                           |

| 2 <sup>4</sup> | 16   | 10 <sup>4</sup> | 10 0111 0001 0000                       |

| $2^{5}$        | 32   | $10^{5}$        | 0×186A0                                 |

| $2^{6}$        | 64   | $10^{6}$        | 0xF4240                                 |

| $2^{7}$        | 128  | $10^{7}$        | 0×989680                                |

| 2 <sup>8</sup> | 256  | 10 <sup>8</sup> | 0x5F5E100                               |

| $2^{9}$        | 512  | $10^{9}$        | 0x369ACA00                              |

| $2^{10}$       | 1024 | 10 <sup>1</sup> | 0 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|                |      |                 |                                         |

. . .

MIN-Fakultät Fachbereich Informatik

64-040 Rechnerstrukturen

# Potenztabellen: Beispiel

#### Beispiel: Umwandlung Dezimal- in Dualzahl

$\begin{array}{l} \text{(Verwendung von Potenztabelle 1.3.1.1/1)} \\ \text{Annahme: } z = (163)_{10} \\ \hline 163 \\ \underline{-128} \quad (2^7) \\ \hline 35 \\ \underline{-32} \quad (2^5) \\ \hline 10.00000 \\ \hline 3 \\ \underline{-2} \quad (2^1) \\ \hline 1 \\ \hline 0 \\ \hline 1010.0011 \\ \hline \end{array}$

$(163)_{10} \longleftrightarrow (1010.0011)_2$

A. Mäder ロ タ - ま タスで 151

5.3 Zahldarstellung - Umrechnung zwischen verschiedenen Base

64-040 Rechnerstrukturer

# Divisionsrestverfahren

- Division der umzuwandelnden Zahl im Ausgangssystem durch die Basis des Zielsystems

- ► Erneute Division des ganzzahligen Ergebnisses (ohne Rest) durch die Basis des Zielsystems, bis kein ganzzahliger Divisionsrest mehr bleibt

- ► Beispiel:

MIN-Fakultät Fachbereich Informatik

5.3 Zahldarstellung - Umrechnung zwischen verschiedenen Basen

-040 Rechnerstrukturen

# Potenztabellen: Beispiel (cont.)

#### Beispiel: Umformung Dual- in Dezimalzahl

7ahldarstellung - Umrechnung zwischen verschiedenen Basen

64-040 Rechnerstrukturen

# Divisionsrestverfahren: Beispiel

#### Beispiel: Umwandlung Dual- in Dezimalzahl:

(wie oben)

$$\begin{array}{ccccc} (1010.0011)_2 : (1010)_2 = 1.0000 & Rest & (11)_2 \stackrel{\frown}{=} (3)_{10} \\ (1.0000)_2 : (1010)_2 = & 1 & Rest & (110)_2 \stackrel{\frown}{=} (6)_{10} \\ (1)_2 : (1010)_2 = & 0 & Rest & (1)_2 \stackrel{\frown}{=} (1)_{10} \end{array}$$

$(1010.0011)_2 \longleftrightarrow (163)_{10}$

Hinweis: Division in Basis b folgt

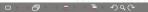

# Demo: Interaktives Skript, stellen2stellen

# Horner-Schema: Beispiel

gegeben:

$$(163)_{10}$$

$163 = (1 \cdot 10 + 6) \cdot 10 + 3$

Umsetzung von Faktoren und Summanden ins Zielzahlensystem:

$$\begin{array}{ccc} (10)_{10} &\longleftrightarrow & (1010)_2 \\ (1)_{10} &\longleftrightarrow & (0001)_2 \\ (6)_{10} &\longleftrightarrow & (0110)_2 \\ (3)_{10} &\longleftrightarrow & (0011)_2 \end{array}$$

Durchführung der arithmetischen Operation

$$\begin{array}{rcl} 0001 \cdot 1010 & = & 1010 \\ & + & 0110 \\ \hline & \overline{1.0000} \, \cdot \, 1010 \, = \, 1010.0000 \\ & + & 0011 \\ \hline & \overline{1010.0011} \end{array}$$

MIN-Fakultät

### Horner-Schema

▶ Darstellung einer Potenzsumme durch ineinander verschachtelte Faktoren

$$|z| = \sum_{i=0}^{n-1} a_i \cdot b^i = (\dots(((a_{n-1} \cdot b + a_{n-2})) \cdot b + a_{n-3}) \cdot b + \dots + a_1) \cdot b + a_0$$

#### Vorgehensweise:

- ▶ Darstellung der umzuwandelnden Zahl im Horner-Schema

- ▶ Durchführung der auftretenden Multiplikationen und Additionen im Zielsystem

MIN-Fakultät

Universität Hamburg

# Horner-Schema: Beispiel (cont.)

Rückumwandlung von Dual- in Dezimalzahl

$$(1010.0011)_2 = (((((((1 \cdot 10_2) + 0) \cdot 10_2 + 1) \cdot 10_2 + 0) \cdot 10_2 + 0) \cdot 10_2 + 0) \cdot 10_2 + 1) \cdot 10_2 + 1$$

Umsetzung von Faktoren und Summanden

$$\begin{array}{c} (0)_2 \longleftrightarrow (0)_{10} \\ (1)_2 \longleftrightarrow (1)_{10} \\ (10)_2 \longleftrightarrow (2)_{10} \end{array}$$

# Horner-Schema: Beispiel (cont.)

Berechnung:

A. Mäder

4 Zahldarstellung - Zahlenhereich und Präfixe

64-040 Rechnerstrukture

### Präfixe

Für die vereinfachte Schreibweise von großen bzw. sehr kleinen Werten ist die Präfixangabe als Abkürzung von Zehnerpotenzen üblich. Beispiele:

- ► Lichtgeschwindigkeit: 300 000 km/s = 30 cm/ns

- ► Ruheenergie des Elektrons: 0,51 MeV

- ▶ Strukturbreite heutiger Mikrochips: 32 nm

- usw.

Es gibt entsprechende Präfixe auch für das Dualsystem. Dazu werden Vielfache von  $2^{10}=1024\approx 1000$  verwendet.

MIN-Fakultät Fachbereich Informatik

5.4 Zahldarstellung - Zahlenbereich und Präfix

4-040 Rechnerstrukturen

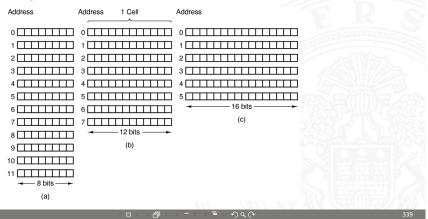

# Zahlenbereich bei fester Wortlänge

| Anzahl der Bits | =          | Zahlenbereich jeweils von 0 bis $(2^n - 1)$ |

|-----------------|------------|---------------------------------------------|

| 4-bit           | $2^4 =$    | 16                                          |

| 8-bit           | $2^8 =$    | 256                                         |

| 10-bit          | $2^{10} =$ | 1024                                        |

| 12-bit          | $2^{12} =$ | 4 096                                       |

| 16-bit          | $2^{16} =$ | 65 536                                      |

| 20-bit          | $2^{20} =$ | 1 048 576                                   |

| 24-bit          | $2^{24} =$ | 16 777 216                                  |

| 32-bit          | $2^{32} =$ | 4 294 967 296                               |

| 48-bit          | $2^{48} =$ | 281 474 976 710 656                         |

| 64-bit          | $2^{64} =$ | 18 446 744 073 709 551 616                  |

MIN-Fakultät ||

Fachbereich Informatik ||

Zahldarstellung - Zahlenbereich und Präfixe

64-040 Rechnerstrukturen

# Präfixe für Einheiten im Dezimalsystem

| Faktor    | Name  | Symbol | Faktor     | Name  | Symbo |

|-----------|-------|--------|------------|-------|-------|

| $10^{24}$ | yotta | Υ      | $10^{-24}$ | yocto | у     |

| $10^{21}$ | zetta | Z      | $10^{-21}$ | zepto | Z     |

| $10^{18}$ | exa   | Е      | $10^{-18}$ | atto  | a     |

| $10^{15}$ | peta  | Р      | $10^{-15}$ | femto | f     |

| $10^{12}$ | tera  | Т      | $10^{-12}$ | pico  | р     |

| $10^{9}$  | giga  | G      | $10^{-9}$  | nano  | n     |

| $10^{6}$  | mega  | М      | $10^{-6}$  | micro | $\mu$ |

| $10^{3}$  | kilo  | K      | $10^{-3}$  | milli | m     |

| $10^{2}$  | hecto | h      | $10^{-2}$  | centi | С     |

| $10^{1}$  | deka  | da     | $10^{-1}$  | dezi  | d     |

|           |       |        |            |       |       |

# Präfixe für Einheiten im Dualsystem

| Faktor          | Name | Symbol | Langname   |

|-----------------|------|--------|------------|

| $2^{60}$        | exbi | Ei     | exabinary  |

| $2^{50}$        | pebi | Pi     | petabinary |

| 2 <sup>40</sup> | tebi | Ti     | terabinary |

| $2^{30}$        | gibi | Gi     | gigabinary |

| $2^{20}$        | mebi | Mi     | megabinary |

| $2^{10}$        | kibi | Ki     | kilobinary |

Beispiele: 1 kibibit = 1024 bit

1 kilobit = 1000 bit 1 megibit = 1048576 bit1 gibibit = 1073741824 bit

IEC-60027-2, Letter symbols to be used in electrical technology

5 5 Zahldarstellung - Festkommazahlen

64-040 Rechnerstrukturer

# Festkommadarstellung

Darstellung von **gebrochenen Zahlen** als Erweiterung des Stellenwertsystems durch Erweiterung des Laufindex zu negativen Werten:

$$|z| = \sum_{i=0}^{n-1} a_i \cdot b^i + \sum_{i=-\infty}^{i=-1} a_i \cdot b^i$$

$$= \sum_{i=-\infty}^{n-1} a_i \cdot b^i$$

mit  $a_i \in N$  und  $0 \le a_i < b$ .

► Der erste Summand bezeichnet den ganzzahligen Anteil, während der zweite Summand für den gebrochenen Anteil steht.

5.4 Zahldarstellung - Zahlenbereich und Präfix

4-040 Rechnerstrukturen

# Präfixe für Einheiten im Dualsystem

In der Praxis werden die offiziellen Präfixe nicht immer sauber verwendet. Meistens ergibt sich die Bedeutung aber aus dem Kontext. Bei Speicherbausteinen sind Zweierpotenzen üblich, bei Festplatten dagegen die dezimale Angabe.

- ▶ DRAM-Modul mit 1 GB Kapazität: gemeint sind 2<sup>30</sup> Bytes

- ► Flash-Speicherkarte 4 GB Kapazität: gemeint sind 2<sup>32</sup> Bytes

- ► Festplatte mit Angabe 1 TB Kapazität: typisch 10<sup>12</sup> Bytes

- ▶ die tatsächliche angezeigte verfügbare Kapazität ist oft geringer, weil das jeweilige Dateisystem Platz für seine eigenen Verwaltungsinformationen belegt.

A. Mäder

> 〈昼 > 〈三 > 〈 Ē > 夕 o

Oniversität Hambarg

64-040 Rechnerstrukturen

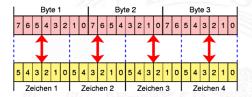

# Nachkommastellen im Dualsystem

$ightharpoonup 2^{-1} = 0.5$

$2^{-2} = 0.25$

$2^{-3} = 0.125$

$2^{-4} = 0.0625$

$2^{-5} = 0.03125$

$2^{-6} = 0.015625$

$2^{-7} = 0.0078125$

. . .

▶ alle Dualbrüche sind im Dezimalsystem exakt darstellbar (d.h. mit endlicher Wortlänge)

# Beispiel: Umrechnung dezimal 0.3 nach dual

Betrachtung von gebrochenen Zahlen im Dualsystem:

#### Beispiel:

$$(0,3)_{10} = 0 \cdot 2^{-1} + 1 \cdot 2^{-2} + 0 \cdot 2^{-3} + 0 \cdot 2^{-4} + 1 \cdot 2^{-5} + 1 \cdot 2^{-6} + \dots = 2^{-2} + 2^{-5} + 2^{-6} + 2^{-9} + \dots = (0,0\overline{1001})_2$$

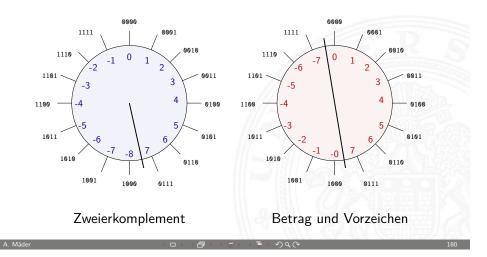

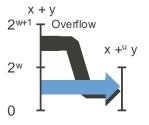

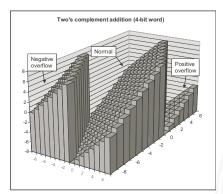

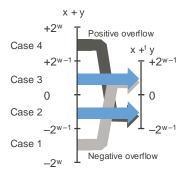

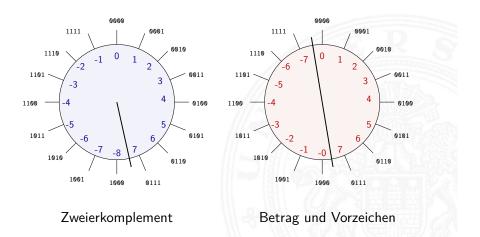

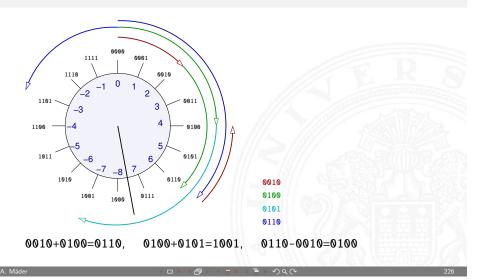

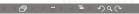

# Darstellung negativer Zahlen

Drei gängige Varianten zur Darstellung negativer Zahlen:

- 1. Betrag und Vorzeichen

- 2. Exzess-Codierung (Offset-basiert)

- 3. Komplementdarstellung

- ► Integerrechnung häufig im Zweierkomplement

- ► Gleitkommadarstellung mit Betrag und Vorzeichen

# Beispiel: Dezimalbrüche, eine Nachkommastelle

- ▶ gebrochene Zahlen können je nach Wahl der Basis evtl. nur als unendliche periodische Brüche dargestellt werden.

- ▶ insbesondere: viele endliche Dezimalbrüche erfordern im Dualsystem unendliche periodische Brüche.

| B=10 | B=2                   | B=2   | B=10  |

|------|-----------------------|-------|-------|

| 0,1  | 0,00011               | 0,001 | 0,125 |

| 0,2  | $0, \overline{0011}$  | 0,010 | 0,250 |

| 0,3  | $0, \overline{01001}$ | 0,011 | 0,375 |

| 0,4  | $0,\overline{0110}$   | 0,100 | 0,5   |

| 0,5  | 0,1                   | 0,101 | 0,625 |

| 0,6  | $0, \overline{1001}$  | 0,110 | 0,750 |

| 0,7  | $0, 1\overline{0110}$ | 0,111 | 0,875 |

| 0,8  | $0,\overline{1100}$   |       |       |

| 0,9  | $0, 1\overline{1100}$ |       |       |

|      | '                     |       |       |

# Darstellung negativer Zahlen: Beispiele