|  |

DescriptionThis applet demonstrates the Quicksort Algorithm

running on the Pipelined Femtojava Processor.

Please see the

Femtojava pipeline overview page

for details about the RT-level hardware structure

and the design flow and tools.

DescriptionThis applet demonstrates the Quicksort Algorithm

running on the Pipelined Femtojava Processor.

Please see the

Femtojava pipeline overview page

for details about the RT-level hardware structure

and the design flow and tools.

The applet directly loads the quicksort algorithm into the program ROM and some initial (unsorted) data into the main memory RAM. Again, the binary memory data dumps (mif files for RAM and ROM) were generated using the Sashimi Tool.

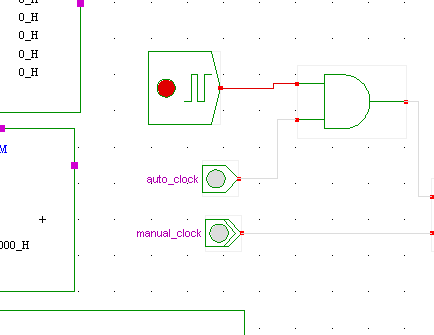

As explained above, the schematics was generated automatically from the synthesized processor description. While there are a lot of components, all interesting components are in the top left corner. Therefore, please use the 'zoom region' to first zoom into the top-left corner of the schematics before running the simulation. You might also want to open the applet in an external window (popup > window > open external window) to enlarge the window. Then use the popup-menu ('edit') on the ROM component to open the window with preferences. The default (romadd.mif) its a simple program based on the following code:

Now, you can start the simulation. If you want that the simulation runs automatic, just turn on the auto_clock, otherwise, you can control the clocks just clicking in manual_clock button.

The sort program needs about 5800 cicles to finish.

The result can be found in the RAM memory, starting at address 20.

The sort program needs about 5800 cicles to finish.

The result can be found in the RAM memory, starting at address 20.

Run the applet | Run the editor (via Webstart)